1 Montgomery Modular Multiplication in Hard- ware

1 Montgomery Modular Multiplication in Hard- ware

1 Montgomery Modular Multiplication in Hard- ware

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

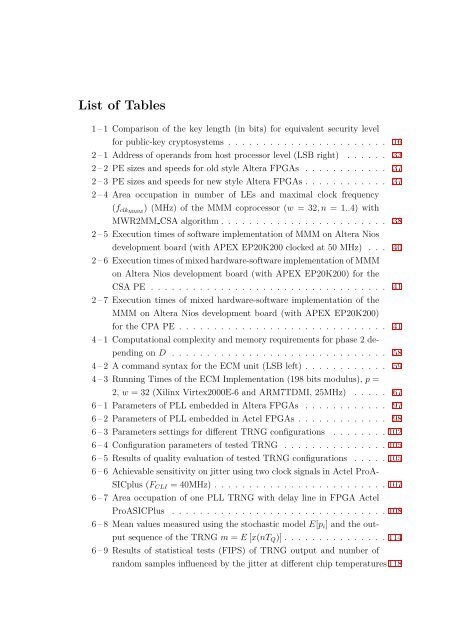

List of Tables<br />

1 – 1 Comparison of the key length (<strong>in</strong> bits) for equivalent security level<br />

for public-key cryptosystems . . . . . . . . . . . . . . . . . . . . . . . 16<br />

2 – 1 Address of operands from host processor level (LSB right) . . . . . . 33<br />

2 – 2 PE sizes and speeds for old style Altera FPGAs . . . . . . . . . . . . 37<br />

2 – 3 PE sizes and speeds for new style Altera FPGAs . . . . . . . . . . . . 37<br />

2 – 4 Area occupation <strong>in</strong> number of LEs and maximal clock frequency<br />

(fclkMMM ) (MHz) of the MMM coprocessor (w = 32, n = 1..4) with<br />

MWR2MM CSA algorithm . . . . . . . . . . . . . . . . . . . . . . . . 38<br />

2 – 5 Execution times of soft<strong>ware</strong> implementation of MMM on Altera Nios<br />

development board (with APEX EP20K200 clocked at 50 MHz) . . . 40<br />

2 – 6 Execution times of mixed hard<strong>ware</strong>-soft<strong>ware</strong> implementation of MMM<br />

on Altera Nios development board (with APEX EP20K200) for the<br />

CSA PE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41<br />

2 – 7 Execution times of mixed hard<strong>ware</strong>-soft<strong>ware</strong> implementation of the<br />

MMM on Altera Nios development board (with APEX EP20K200)<br />

for the CPA PE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41<br />

4 – 1 Computational complexity and memory requirements for phase 2 de-<br />

pend<strong>in</strong>g on D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58<br />

4 – 2 A command syntax for the ECM unit (LSB left) . . . . . . . . . . . . 59<br />

4 – 3 Runn<strong>in</strong>g Times of the ECM Implementation (198 bits modulus), p =<br />

2, w = 32 (Xil<strong>in</strong>x Virtex2000E-6 and ARM7TDMI, 25MHz) . . . . . 67<br />

6 – 1 Parameters of PLL embedded <strong>in</strong> Altera FPGAs . . . . . . . . . . . . 97<br />

6 – 2 Parameters of PLL embedded <strong>in</strong> Actel FPGAs . . . . . . . . . . . . . 98<br />

6 – 3 Parameters sett<strong>in</strong>gs for different TRNG configurations . . . . . . . . 102<br />

6 – 4 Configuration parameters of tested TRNG . . . . . . . . . . . . . . . 105<br />

6 – 5 Results of quality evaluation of tested TRNG configurations . . . . . 105<br />

6 – 6 Achievable sensitivity on jitter us<strong>in</strong>g two clock signals <strong>in</strong> Actel ProA-<br />

SICplus (FCLI = 40MHz) . . . . . . . . . . . . . . . . . . . . . . . . . 107<br />

6 – 7 Area occupation of one PLL TRNG with delay l<strong>in</strong>e <strong>in</strong> FPGA Actel<br />

ProASICPlus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108<br />

6 – 8 Mean values measured us<strong>in</strong>g the stochastic model E[pi] and the out-<br />

put sequence of the TRNG m = E [x(nTQ)] . . . . . . . . . . . . . . . 114<br />

6 – 9 Results of statistical tests (FIPS) of TRNG output and number of<br />

random samples <strong>in</strong>fluenced by the jitter at different chip temperatures 118