Christoph Haederli - Les thèses en ligne de l'INP - Institut National ...

Christoph Haederli - Les thèses en ligne de l'INP - Institut National ...

Christoph Haederli - Les thèses en ligne de l'INP - Institut National ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

ML Converter Topologies 35<br />

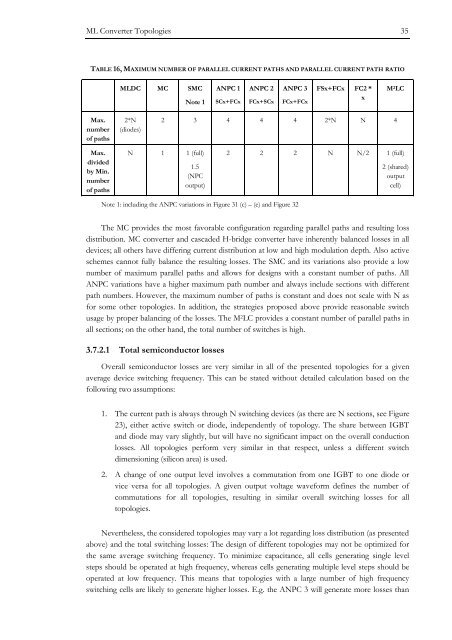

TABLE 16, MAXIMUM NUMBER OF PARALLEL CURRENT PATHS AND PARALLEL CURRENT PATH RATIO<br />

MLDC MC SMC<br />

Note 1<br />

ANPC 1<br />

SCx+FCx<br />

ANPC 2<br />

FCx+SCx<br />

ANPC 3<br />

FCx+FCx<br />

FSx+FCx FC2 *<br />

x<br />

M 2 LC<br />

Max.<br />

number<br />

of paths<br />

2*N<br />

(dio<strong>de</strong>s)<br />

2 3 4 4 4 2*N N 4<br />

Max.<br />

divi<strong>de</strong>d<br />

by Min.<br />

number<br />

of paths<br />

N 1 1 (full)<br />

1.5<br />

(NPC<br />

output)<br />

2 2 2 N N/2 1 (full)<br />

2 (shared)<br />

output<br />

cell)<br />

Note 1: including the ANPC variations in Figure 31 (c) – (e) and Figure 32<br />

The MC provi<strong>de</strong>s the most favorable configuration regarding parallel paths and resulting loss<br />

distribution. MC converter and casca<strong>de</strong>d H-bridge converter have inher<strong>en</strong>tly balanced losses in all<br />

<strong>de</strong>vices; all others have differing curr<strong>en</strong>t distribution at low and high modulation <strong>de</strong>pth. Also active<br />

schemes cannot fully balance the resulting losses. The SMC and its variations also provi<strong>de</strong> a low<br />

number of maximum parallel paths and allows for <strong>de</strong>signs with a constant number of paths. All<br />

ANPC variations have a higher maximum path number and always inclu<strong>de</strong> sections with differ<strong>en</strong>t<br />

path numbers. However, the maximum number of paths is constant and does not scale with N as<br />

for some other topologies. In addition, the strategies proposed above provi<strong>de</strong> reasonable switch<br />

usage by proper balancing of the losses. The M 2 LC provi<strong>de</strong>s a constant number of parallel paths in<br />

all sections; on the other hand, the total number of switches is high.<br />

3.7.2.1 Total semiconductor losses<br />

Overall semiconductor losses are very similar in all of the pres<strong>en</strong>ted topologies for a giv<strong>en</strong><br />

average <strong>de</strong>vice switching frequ<strong>en</strong>cy. This can be stated without <strong>de</strong>tailed calculation based on the<br />

following two assumptions:<br />

1. The curr<strong>en</strong>t path is always through N switching <strong>de</strong>vices (as there are N sections, see Figure<br />

23), either active switch or dio<strong>de</strong>, in<strong>de</strong>p<strong>en</strong>d<strong>en</strong>tly of topology. The share betwe<strong>en</strong> IGBT<br />

and dio<strong>de</strong> may vary slightly, but will have no significant impact on the overall conduction<br />

losses. All topologies perform very similar in that respect, unless a differ<strong>en</strong>t switch<br />

dim<strong>en</strong>sioning (silicon area) is used.<br />

2. A change of one output level involves a commutation from one IGBT to one dio<strong>de</strong> or<br />

vice versa for all topologies. A giv<strong>en</strong> output voltage waveform <strong>de</strong>fines the number of<br />

commutations for all topologies, resulting in similar overall switching losses for all<br />

topologies.<br />

Nevertheless, the consi<strong>de</strong>red topologies may vary a lot regarding loss distribution (as pres<strong>en</strong>ted<br />

above) and the total switching losses: The <strong>de</strong>sign of differ<strong>en</strong>t topologies may not be optimized for<br />

the same average switching frequ<strong>en</strong>cy. To minimize capacitance, all cells g<strong>en</strong>erating single level<br />

steps should be operated at high frequ<strong>en</strong>cy, whereas cells g<strong>en</strong>erating multiple level steps should be<br />

operated at low frequ<strong>en</strong>cy. This means that topologies with a large number of high frequ<strong>en</strong>cy<br />

switching cells are likely to g<strong>en</strong>erate higher losses. E.g. the ANPC 3 will g<strong>en</strong>erate more losses than