AMBA Design Kit Technical Reference Manual - ARM Information ...

AMBA Design Kit Technical Reference Manual - ARM Information ...

AMBA Design Kit Technical Reference Manual - ARM Information ...

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

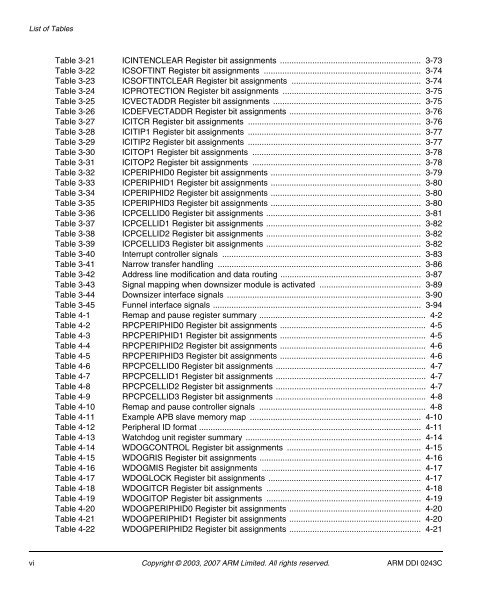

List of TablesTable 3-21 ICINTENCLEAR Register bit assignments ............................................................. 3-73Table 3-22 ICSOFTINT Register bit assignments .................................................................... 3-74Table 3-23 ICSOFTINTCLEAR Register bit assignments ........................................................ 3-74Table 3-24 ICPROTECTION Register bit assignments ............................................................ 3-75Table 3-25 ICVECTADDR Register bit assignments ................................................................ 3-75Table 3-26 ICDEFVECTADDR Register bit assignments ......................................................... 3-76Table 3-27 ICITCR Register bit assignments ........................................................................... 3-76Table 3-28 ICITIP1 Register bit assignments ........................................................................... 3-77Table 3-29 ICITIP2 Register bit assignments ........................................................................... 3-77Table 3-30 ICITOP1 Register bit assignments ......................................................................... 3-78Table 3-31 ICITOP2 Register bit assignments ......................................................................... 3-78Table 3-32 ICPERIPHID0 Register bit assignments ................................................................. 3-79Table 3-33 ICPERIPHID1 Register bit assignments ................................................................. 3-80Table 3-34 ICPERIPHID2 Register bit assignments ................................................................. 3-80Table 3-35 ICPERIPHID3 Register bit assignments ................................................................. 3-80Table 3-36 ICPCELLID0 Register bit assignments ................................................................... 3-81Table 3-37 ICPCELLID1 Register bit assignments ................................................................... 3-82Table 3-38 ICPCELLID2 Register bit assignments ................................................................... 3-82Table 3-39 ICPCELLID3 Register bit assignments ................................................................... 3-82Table 3-40 Interrupt controller signals ...................................................................................... 3-83Table 3-41 Narrow transfer handling ........................................................................................ 3-86Table 3-42 Address line modification and data routing ............................................................. 3-87Table 3-43 Signal mapping when downsizer module is activated ............................................ 3-89Table 3-44 Downsizer interface signals .................................................................................... 3-90Table 3-45 Funnel interface signals .......................................................................................... 3-94Table 4-1 Remap and pause register summary ........................................................................ 4-2Table 4-2 RPCPERIPHID0 Register bit assignments ............................................................... 4-5Table 4-3 RPCPERIPHID1 Register bit assignments ............................................................... 4-5Table 4-4 RPCPERIPHID2 Register bit assignments ............................................................... 4-6Table 4-5 RPCPERIPHID3 Register bit assignments ............................................................... 4-6Table 4-6 RPCPCELLID0 Register bit assignments ................................................................. 4-7Table 4-7 RPCPCELLID1 Register bit assignments ................................................................. 4-7Table 4-8 RPCPCELLID2 Register bit assignments ................................................................. 4-7Table 4-9 RPCPCELLID3 Register bit assignments ................................................................. 4-8Table 4-10 Remap and pause controller signals ........................................................................ 4-8Table 4-11 Example APB slave memory map .......................................................................... 4-10Table 4-12 Peripheral ID format ................................................................................................ 4-11Table 4-13 Watchdog unit register summary ............................................................................ 4-14Table 4-14 WDOGCONTROL Register bit assignments .......................................................... 4-15Table 4-15 WDOGRIS Register bit assignments ...................................................................... 4-16Table 4-16 WDOGMIS Register bit assignments ..................................................................... 4-17Table 4-17 WDOGLOCK Register bit assignments .................................................................. 4-17Table 4-18 WDOGITCR Register bit assignments ................................................................... 4-18Table 4-19 WDOGITOP Register bit assignments ................................................................... 4-19Table 4-20 WDOGPERIPHID0 Register bit assignments ......................................................... 4-20Table 4-21 WDOGPERIPHID1 Register bit assignments ......................................................... 4-20Table 4-22 WDOGPERIPHID2 Register bit assignments ......................................................... 4-21vi Copyright © 2003, 2007 <strong>ARM</strong> Limited. All rights reserved. <strong>ARM</strong> DDI 0243C