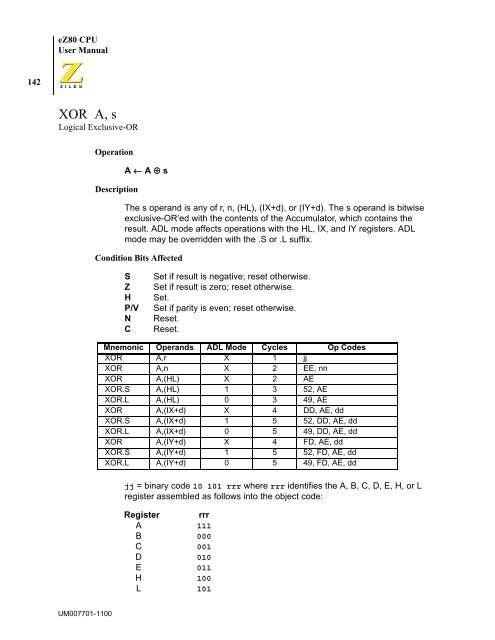

<strong>eZ80</strong> <strong>CPU</strong> User Manual 142 XOR A, s Logical Exclusive-OR Operation Description A ← A ⊕ s The s operand is any of r, n, (HL), (IX+d), or (IY+d). The s operand is bitwise exclusive-OR’ed with the contents of the Accumulator, which contains the result. ADL mode affects operations with the HL, IX, and IY registers. ADL mode may be overridden with the .S or .L suffix. Condition Bits Affected S Z H P/V N C Set if result is negative; reset otherwise. Set if result is zero; reset otherwise. Set. Set if parity is even; reset otherwise. Reset. Reset. Mnemonic Operands ADL Mode Cycles Op Codes XOR A,r X 1 jj XOR A,n X 2 EE, nn XOR A,(HL) X 2 AE XOR.S A,(HL) 1 3 52, AE XOR.L A,(HL) 0 3 49, AE XOR A,(IX+d) X 4 DD, AE, dd XOR.S A,(IX+d) 1 5 52, DD, AE, dd XOR.L A,(IX+d) 0 5 49, DD, AE, dd XOR A,(IY+d) X 4 FD, AE, dd XOR.S A,(IY+d) 1 5 52, FD, AE, dd XOR.L A,(IY+d) 0 5 49, FD, AE, dd jj = binary code 10 101 rrr where rrr identifies the A, B, C, D, E, H, or L register assembled as follows into the object code: Register rrr A 111 B 000 C 001 D 010 E 011 H 100 L 101 UM007701-1100

<strong>eZ80</strong> <strong>CPU</strong> User Manual 143 Op Code Maps UPPER NIBBLE (HEX) Table 7. Op Code Map (First Op Code) LOWER NIBBLE (HEX) 0 1 2 3 4 5 6 7 8 9 A B C D E F 0 NOP LD LD INC INC DEC LD RLCA EX ADD LD DEC INC DEC LD RRCA BC,nn (BC),A BC B B B,n AF,AF’ HL,BC A,(BC) BC C C C,n 1 DJNZ LD LD INC INC DEC LD RLA JR ADD LD DEC INC DEC LD RRA d DE,nn (DE),A DE D D D,n d HL,DE A,(DE) DE E E E,n 2 JR LD LD INC INC DEC LD DAA JR ADD LD DEC INC DEC LD CPL NZ,d HL,nn (nn),HL HL H H H,n Z,d HL,HL (HL),nn HL L L L,n 3 JR LD LD INC INC DEC LD SCF JR ADD LD DEC INC DEC LD CCF NC,d SP,nn (nn),A SP (HL) (HL) (HL),n C,d HL,SP A,(nn) SP A A A,n 4 .SIS LD LD LD LD LD LD LD LD .LIS LD LD LD LD LD LD prefix B,C B,D B,E B,H B,L B,(HL) C,A C,B prefix C,D C,E C,H C,L C,(HL) C,A 5 LD LD .SIL LD LD LD LD LD LD LD LD .LIL LD LD LD LD D,B D,C prefix D,E D,H D,L D,(HL) D,A E,B E,C E,D prefix E,H E,L E,(HL) E,A 6 LD LD LD LD LD LD LD LD LD LD LD LD LD LD LD LD H,B H,C H,D H,E H,H H,L H,(HL) H,A L,B L,C L,D L,E L,H L,L L,(HL) L,A 7 LD LD LD LD LD LD HALT LD LD LD LD LD LD LD LD LD (HL),B (HL),C (HL),D (HL),E (HL),H (HL),L (HL),A A,B A,C A,D A,E A,H A,L A,(HL) A,A 8 ADD ADD ADD ADD ADD ADD ADD ADD ADC ADC ADC ADC ADC ADC ADC ADC A,B A,C A,D A,E A,H A,L A,(HL) A,A A,B A,C A,D A,E A,H A,L A,(HL) A,A 9 SUB SUB SUB SUB SUB SUB SUB SUB SBC SBC SBC SBC SBC SBC SBC SBC A,B A,C A,D A,E A,H A,L A,(HL) A,A A,B A,C A,D A,E A,H A,L A,(HL) A,A A AND AND AND AND AND AND AND AND XOR XOR XOR XOR XOR XOR XOR XOR A,B A,C A,D A,E A,H A,L A,(HL) A,A A,B A,C A,D A,E A,H A,L A,(HL) A,A B OR OR OR OR OR OR OR OR CP CP CP CP CP CP CP CP A,B A,C A,D A,E A,H A,L A,(HL) A,A A,B A,C A,D A,E A,H A,L A,(HL) A,A C RET POP JP JP CALL PUSH ADD RST RET RET JP Table 8 CALL CALL ADC RST NZ BC NZ,nn nn NZ,nn BC A,n 0 Z Z,nn Z,nn nn A,n 8 D RET POP JP OUT CALL PUSH SUB RST RET EXX JP IN CALL Table9 SBC RST NZ DE NC,nn (n),A NC,nn DE A,n 10H C C,nn A,(n) C,nn A,n 18H E RET POP JP EX CALL PUSH AND RST RET JP JP EX CALL Table 10 XOR RST PO HL PO,nn (SP),HL PO,nn HL A,n 20 PE (HL) PE,nn DE,HL PE,nn A,n 28H F RET POP JP DI CALL PUSH OR RST RET LD JP EI CALL Table11 CP RST P AF P,nn P,nn AF A,n 30H M SP,HL M,nn M,nn A,n 38H 0 1 2 3 4 5 6 7 8 9 A B C D E F Note: n = 8-bit data nn = 16-bit addr or data d = signed 8-bit displacement Upper Op Code Nibble First Operand Lower Op Code Nibble A 4 AND A,H Mnemonic Second Operand UM007701-1100

- Page 1 and 2:

eZ80 CPU User Manual UM007701-1100

- Page 3 and 4:

eZ80 CPU User Manual i Table of Con

- Page 5 and 6:

eZ80 CPU User Manual iii INIR . . .

- Page 7 and 8:

eZ80 CPU User Manual v List of Tabl

- Page 9 and 10:

eZ80 CPU User Manual 1 Introduction

- Page 11 and 12:

eZ80 CPU User Manual 3 In ADL mode,

- Page 13 and 14:

eZ80 CPU User Manual 5 CPU Response

- Page 15 and 16:

eZ80 CPU User Manual 7 I/O Space A

- Page 17 and 18:

eZ80 CPU User Manual 9 Changing the

- Page 19 and 20:

eZ80 CPU User Manual 11 Table 4. RE

- Page 21 and 22:

eZ80 CPU User Manual 13 Suffixes .I

- Page 23 and 24:

eZ80 CPU User Manual 15 Carry Flag

- Page 25 and 26:

eZ80 CPU User Manual 17 For compare

- Page 27 and 28:

eZ80 CPU User Manual 19 ADC HL, ss

- Page 29 and 30:

eZ80 CPU User Manual 21 ADD rr, ss

- Page 31 and 32:

eZ80 CPU User Manual 23 BIT b, m Te

- Page 33 and 34:

eZ80 CPU User Manual 25 CALL cc, Mm

- Page 35 and 36:

eZ80 CPU User Manual 27 CCF Complem

- Page 37 and 38:

eZ80 CPU User Manual 29 CPD Compare

- Page 39 and 40:

eZ80 CPU User Manual 31 CPI Compare

- Page 41 and 42:

eZ80 CPU User Manual 33 CPL Complem

- Page 43 and 44:

eZ80 CPU User Manual 35 DEC qq Decr

- Page 45 and 46:

eZ80 CPU User Manual 37 DI Disable

- Page 47 and 48:

eZ80 CPU User Manual 39 EI Enable I

- Page 49 and 50:

eZ80 CPU User Manual 41 EX DE, HL E

- Page 51 and 52:

eZ80 CPU User Manual 43 EXX Exchang

- Page 53 and 54:

eZ80 CPU User Manual 45 IM n Set In

- Page 55 and 56:

eZ80 CPU User Manual 47 IN r, (C) I

- Page 57 and 58:

eZ80 CPU User Manual 49 INC qq Incr

- Page 59 and 60:

eZ80 CPU User Manual 51 IND Input a

- Page 61 and 62:

eZ80 CPU User Manual 53 IND2R Input

- Page 63 and 64:

eZ80 CPU User Manual 55 INDMR Input

- Page 65 and 66:

eZ80 CPU User Manual 57 INI Input a

- Page 67 and 68:

eZ80 CPU User Manual 59 INI2R Input

- Page 69 and 70:

eZ80 CPU User Manual 61 INIMR Input

- Page 71 and 72:

eZ80 CPU User Manual 63 JP (rr) Jum

- Page 73 and 74:

eZ80 CPU User Manual 65 JP cc, Mmn

- Page 75 and 76:

eZ80 CPU User Manual 67 JR cc, d Co

- Page 77 and 78:

eZ80 CPU User Manual 69 LD A, MB Lo

- Page 79 and 80:

eZ80 CPU User Manual 71 LD A, (pp)

- Page 81 and 82:

eZ80 CPU User Manual 73 LD (HL), tt

- Page 83 and 84:

eZ80 CPU User Manual 75 Operation D

- Page 85 and 86:

eZ80 CPU User Manual 77 LD (Mmn), A

- Page 87 and 88:

eZ80 CPU User Manual 79 LD (pp), A

- Page 89 and 90:

eZ80 CPU User Manual 81 LD R, A Loa

- Page 91 and 92:

eZ80 CPU User Manual 83 LD r, r’

- Page 93 and 94:

eZ80 CPU User Manual 85 LD SP, rr L

- Page 95 and 96:

eZ80 CPU User Manual 87 LD tt,(ii)

- Page 97 and 98:

eZ80 CPU User Manual 89 LD (uu), r

- Page 99 and 100: eZ80 CPU User Manual 91 LEA tt, IX+

- Page 101 and 102: eZ80 CPU User Manual 93 OR A, s Log

- Page 103 and 104: eZ80 CPU User Manual 95 OTDM Output

- Page 105 and 106: eZ80 CPU User Manual 97 OTDR Output

- Page 107 and 108: eZ80 CPU User Manual 99 OTIM Output

- Page 109 and 110: eZ80 CPU User Manual 101 OTIR Outpu

- Page 111 and 112: eZ80 CPU User Manual 103 OUTD Outpu

- Page 113 and 114: eZ80 CPU User Manual 105 OUT (n), A

- Page 115 and 116: eZ80 CPU User Manual 107 OUTI Outpu

- Page 117 and 118: eZ80 CPU User Manual 109 PEA IX+d P

- Page 119 and 120: eZ80 CPU User Manual 111 POP vv Pop

- Page 121 and 122: eZ80 CPU User Manual 113 RES b, m R

- Page 123 and 124: eZ80 CPU User Manual 115 RET cc Con

- Page 125 and 126: eZ80 CPU User Manual 117 RETN Retur

- Page 127 and 128: eZ80 CPU User Manual 119 RLCA Rotat

- Page 129 and 130: eZ80 CPU User Manual 121 RLD Rotate

- Page 131 and 132: eZ80 CPU User Manual 123 RRA Rotate

- Page 133 and 134: eZ80 CPU User Manual 125 RRC m Rota

- Page 135 and 136: eZ80 CPU User Manual 127 RR m Rotat

- Page 137 and 138: eZ80 CPU User Manual 129 RST n Rest

- Page 139 and 140: eZ80 CPU User Manual 131 SBC HL, ss

- Page 141 and 142: eZ80 CPU User Manual 133 SET b, m S

- Page 143 and 144: eZ80 CPU User Manual 135 SLP Sleep

- Page 145 and 146: eZ80 CPU User Manual 137 SRL m Shif

- Page 147 and 148: eZ80 CPU User Manual 139 SUB A, s S

- Page 149: eZ80 CPU User Manual 141 TSTIO n Te

- Page 153 and 154: eZ80 CPU User Manual 145 Table 9. O

- Page 155 and 156: eZ80 CPU User Manual 147 Table 11.

- Page 157 and 158: eZ80 CPU User Manual 149 Table 13.

- Page 159 and 160: eZ80 CPU User Manual 151 Index A AD

- Page 161 and 162: eZ80 CPU User Manual 153 IND2, 52 I

- Page 163 and 164: eZ80 CPU User Manual 155 OTI2R, 98