Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>eZ80</strong> <strong>CPU</strong><br />

User Manual<br />

91<br />

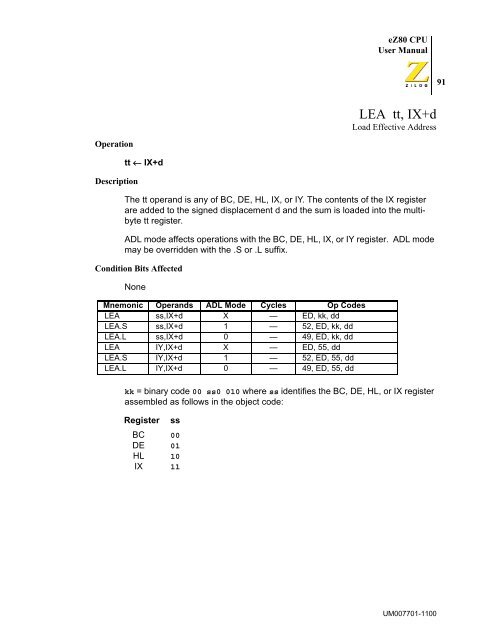

LEA tt, IX+d<br />

Load Effective Address<br />

Operation<br />

Description<br />

tt ← IX+d<br />

The tt operand is any of BC, DE, HL, IX, or IY. The contents of the IX register<br />

are added to the signed displacement d and the sum is loaded into the multibyte<br />

tt register.<br />

ADL mode affects operations with the BC, DE, HL, IX, or IY register. ADL mode<br />

may be overridden with the .S or .L suffix.<br />

Condition Bits Affected<br />

None<br />

Mnemonic Operands ADL Mode Cycles Op Codes<br />

LEA ss,IX+d X — ED, kk, dd<br />

LEA.S ss,IX+d 1 — 52, ED, kk, dd<br />

LEA.L ss,IX+d 0 — 49, ED, kk, dd<br />

LEA IY,IX+d X — ED, 55, dd<br />

LEA.S IY,IX+d 1 — 52, ED, 55, dd<br />

LEA.L IY,IX+d 0 — 49, ED, 55, dd<br />

kk = binary code 00 ss0 010 where ss identifies the BC, DE, HL, or IX register<br />

assembled as follows in the object code:<br />

Register<br />

ss<br />

BC 00<br />

DE 01<br />

HL 10<br />

IX 11<br />

UM007701-1100