Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>eZ80</strong> <strong>CPU</strong><br />

User Manual<br />

56<br />

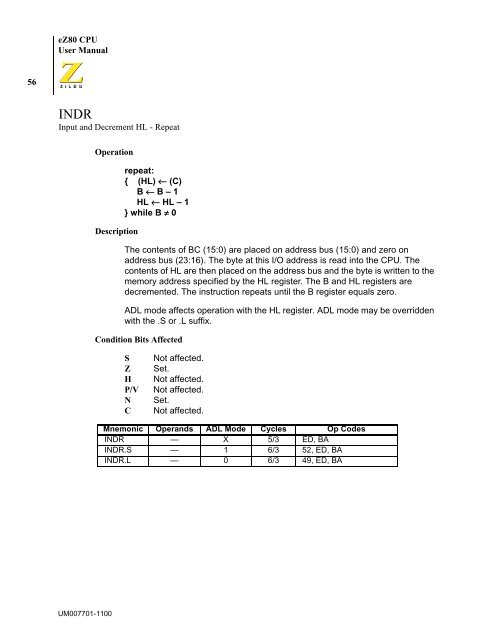

INDR<br />

Input and Decrement HL - Repeat<br />

Operation<br />

Description<br />

repeat:<br />

{ (HL) ← (C)<br />

B ← B – 1<br />

HL ← HL – 1<br />

} while B ≠ 0<br />

The contents of BC (15:0) are placed on address bus (15:0) and zero on<br />

address bus (23:16). The byte at this I/O address is read into the <strong>CPU</strong>. The<br />

contents of HL are then placed on the address bus and the byte is written to the<br />

memory address specified by the HL register. The B and HL registers are<br />

decremented. The instruction repeats until the B register equals zero.<br />

ADL mode affects operation with the HL register. ADL mode may be overridden<br />

with the .S or .L suffix.<br />

Condition Bits Affected<br />

S<br />

Z<br />

H<br />

P/V<br />

N<br />

C<br />

Not affected.<br />

Set.<br />

Not affected.<br />

Not affected.<br />

Set.<br />

Not affected.<br />

Mnemonic Operands ADL Mode Cycles Op Codes<br />

INDR — X 5/3 ED, BA<br />

INDR.S — 1 6/3 52, ED, BA<br />

INDR.L — 0 6/3 49, ED, BA<br />

UM007701-1100