You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>eZ80</strong> <strong>CPU</strong><br />

User Manual<br />

14<br />

Instruction Set<br />

Assembly Language<br />

The <strong>eZ80</strong> assembly language is designed to minimize the number of different<br />

Op Codes corresponding to the set of basic machine operations, as well as to<br />

provide a consistent description of instruction operands. The nomenclature has<br />

been defined with special emphasis on mnemonic values and readability.<br />

The movement of data is indicated by a single Op Code, regardless of whether<br />

the movement is between different registers or between registers and memory<br />

locations.<br />

For example, the first operand of an LD instruction is the destination of the<br />

operation and the second operand is the source of the operation. For example,<br />

LD A, B indicates that the contents of the second operand, register B, are to be<br />

transferred to the first operand, register A. Similarly, LD C, 3FH indicates that<br />

the constant 3FH is to be loaded into Register C. In addition, enclosing an<br />

operand in parentheses indicates a memory location addressed by the contents<br />

of the parentheses. For example, LD HL, (1200) indicates the contents of<br />

memory locations 1200 and 1201 that are to be loaded into the 16-bit register<br />

pair HL. Similarly, LD (IX+6),C indicates that the contents of register C are to be<br />

stored in the memory location addressed by the current value in the 16-bit IX<br />

register plus 6.<br />

<strong>eZ80</strong> Status Indicators<br />

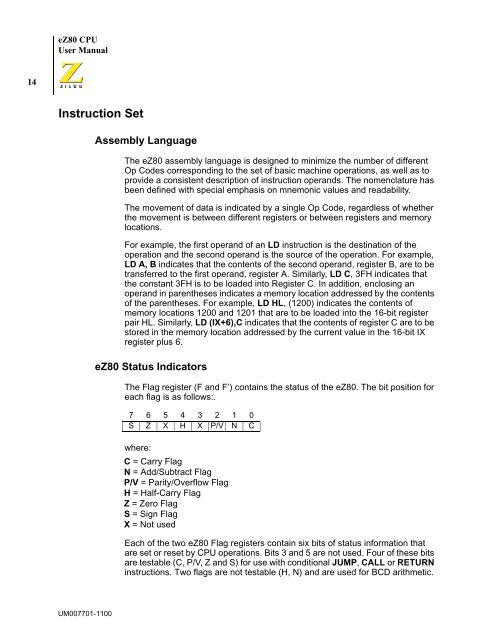

The Flag register (F and F’) contains the status of the <strong>eZ80</strong>. The bit position for<br />

each flag is as follows:.<br />

7 6 5 4 3 2 1 0<br />

S Z X H X P/V N C<br />

where:<br />

C = Carry Flag<br />

N = Add/Subtract Flag<br />

P/V = Parity/Overflow Flag<br />

H = Half-Carry Flag<br />

Z = Zero Flag<br />

S = Sign Flag<br />

X = Not used<br />

Each of the two <strong>eZ80</strong> Flag registers contain six bits of status information that<br />

are set or reset by <strong>CPU</strong> operations. Bits 3 and 5 are not used. Four of these bits<br />

are testable (C, P/V, Z and S) for use with conditional JUMP, CALL or RETURN<br />

instructions. Two flags are not testable (H, N) and are used for BCD arithmetic.<br />

UM007701-1100