Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>eZ80</strong> <strong>CPU</strong><br />

User Manual<br />

15<br />

Carry Flag<br />

The Carry bit is set or reset, depending on the operation that is performed. For<br />

ADD instructions that generate a carry and SUBTRACT instructions that<br />

generate a borrow, the Carry Flag is set to 1. The Carry Flag is reset by an ADD<br />

that does not generate a carry and a subtract that does not generate a borrow.<br />

This saved carry facilitates software routines for extended precision arithmetic.<br />

Also, the DAA instruction sets the Carry Flag to 1 if the conditions for making<br />

the decimal adjustment are met.<br />

For the RLA, RRA, RLS and RRS instructions, the Carry bit is used as a link<br />

between the least-significant bit (LSB) and most-significant bit (MSB) for any<br />

register or memory location. During the RLCA, RLC m and SLA m instructions,<br />

the carry contains the last value shifted out of Bit 7 of any register or memory<br />

location. During the RRCA, RRC m, SRA mand SRL m instructions, the carry<br />

contains the last value shifted out of Bit 0 of any register or memory location.<br />

For the logical instructions AND A s, OR A s, and XOR A s, the carry is reset.<br />

The Carry Flag can also be set (SCF) and complemented (CCF).<br />

Add/Subtract Flag<br />

The Add/Subtract (N) Flag is used by the decimal adjust accumulator<br />

instructions (DAA) to distinguish between ADD and SUBTRACT instructions.<br />

For all ADD instructions, N is set to zero. For all SUBTRACT instructions, N is<br />

set to 1.<br />

Parity/Overflow Flag<br />

The Parity/Overflow (P/V) Flag is set or reset, depending on the operation that<br />

is performed. For arithmetic operations, this flag indicates an overflow condition<br />

when the result in the Accumulator is greater than the maximum possible<br />

number (+127) or is less than the minimum possible number (-128). This<br />

overflow condition can be determined by examining the sign bits of the<br />

operands.<br />

For addition, operands with different signs never causes overflow. When adding<br />

operands with like signs and the result has a different sign, the overflow flag is<br />

set to 1, as shown in the following example.<br />

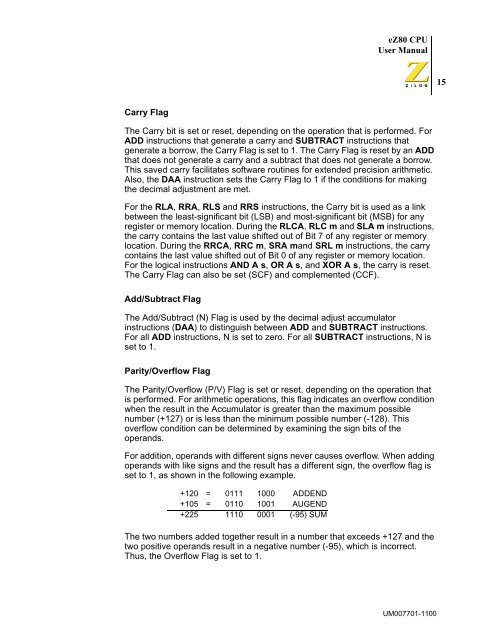

+120 = 0111 1000 ADDEND<br />

+105 = 0110 1001 AUGEND<br />

+225 1110 0001 (-95) SUM<br />

The two numbers added together result in a number that exceeds +127 and the<br />

two positive operands result in a negative number (-95), which is incorrect.<br />

Thus, the Overflow Flag is set to 1.<br />

UM007701-1100