You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>eZ80</strong> <strong>CPU</strong><br />

User Manual<br />

45<br />

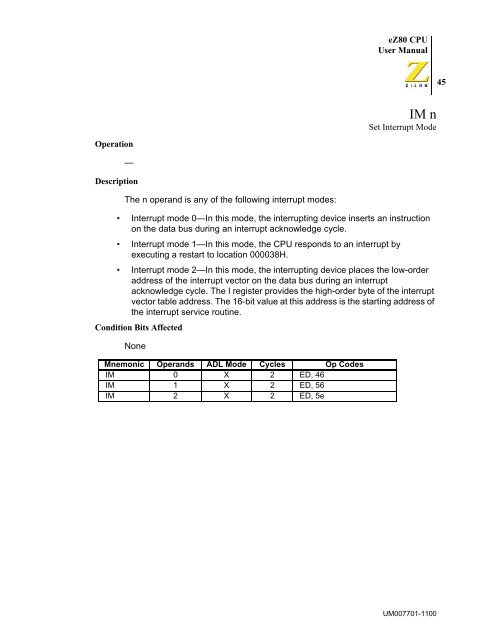

IM n<br />

Set Interrupt Mode<br />

Operation<br />

—<br />

Description<br />

The n operand is any of the following interrupt modes:<br />

• Interrupt mode 0—In this mode, the interrupting device inserts an instruction<br />

on the data bus during an interrupt acknowledge cycle.<br />

• Interrupt mode 1—In this mode, the <strong>CPU</strong> responds to an interrupt by<br />

executing a restart to location 000038H.<br />

• Interrupt mode 2—In this mode, the interrupting device places the low-order<br />

address of the interrupt vector on the data bus during an interrupt<br />

acknowledge cycle. The I register provides the high-order byte of the interrupt<br />

vector table address. The 16-bit value at this address is the starting address of<br />

the interrupt service routine.<br />

Condition Bits Affected<br />

None<br />

Mnemonic Operands ADL Mode Cycles Op Codes<br />

IM 0 X 2 ED, 46<br />

IM 1 X 2 ED, 56<br />

IM 2 X 2 ED, 5e<br />

UM007701-1100