You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

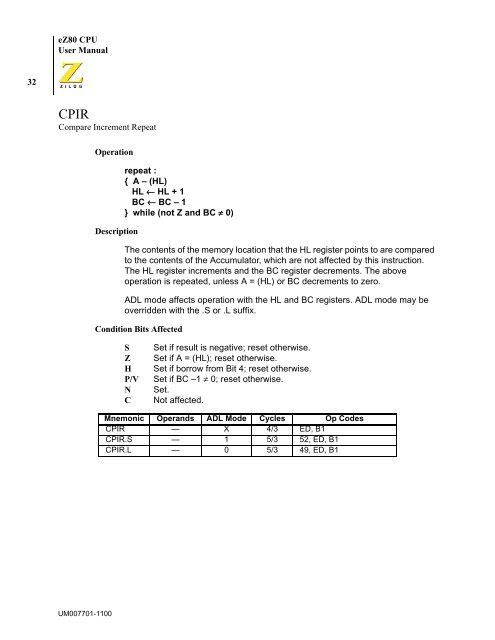

<strong>eZ80</strong> <strong>CPU</strong><br />

User Manual<br />

32<br />

CPIR<br />

Compare Increment Repeat<br />

Operation<br />

Description<br />

repeat :<br />

{ A – (HL)<br />

HL ← HL + 1<br />

BC ← BC – 1<br />

} while (not Z and BC ≠ 0)<br />

The contents of the memory location that the HL register points to are compared<br />

to the contents of the Accumulator, which are not affected by this instruction.<br />

The HL register increments and the BC register decrements. The above<br />

operation is repeated, unless A = (HL) or BC decrements to zero.<br />

ADL mode affects operation with the HL and BC registers. ADL mode may be<br />

overridden with the .S or .L suffix.<br />

Condition Bits Affected<br />

S<br />

Z<br />

H<br />

P/V<br />

N<br />

C<br />

Set if result is negative; reset otherwise.<br />

Set if A = (HL); reset otherwise.<br />

Set if borrow from Bit 4; reset otherwise.<br />

Set if BC –1 ≠ 0; reset otherwise.<br />

Set.<br />

Not affected.<br />

Mnemonic Operands ADL Mode Cycles Op Codes<br />

CPIR — X 4/3 ED, B1<br />

CPIR.S — 1 5/3 52, ED, B1<br />

CPIR.L — 0 5/3 49, ED, B1<br />

UM007701-1100