Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

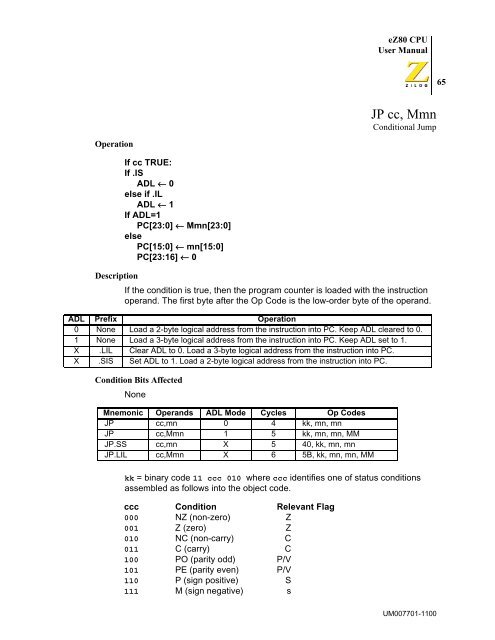

<strong>eZ80</strong> <strong>CPU</strong><br />

User Manual<br />

65<br />

JP cc, Mmn<br />

Conditional Jump<br />

Operation<br />

Description<br />

If cc TRUE:<br />

If .IS<br />

ADL ← 0<br />

else if .IL<br />

ADL ← 1<br />

If ADL=1<br />

PC[23:0] ← Mmn[23:0]<br />

else<br />

PC[15:0] ← mn[15:0]<br />

PC[23:16] ← 0<br />

If the condition is true, then the program counter is loaded with the instruction<br />

operand. The first byte after the Op Code is the low-order byte of the operand.<br />

ADL Prefix Operation<br />

0 None Load a 2-byte logical address from the instruction into PC. Keep ADL cleared to 0.<br />

1 None Load a 3-byte logical address from the instruction into PC. Keep ADL set to 1.<br />

X .LIL Clear ADL to 0. Load a 3-byte logical address from the instruction into PC.<br />

X .SIS Set ADL to 1. Load a 2-byte logical address from the instruction into PC.<br />

Condition Bits Affected<br />

None<br />

Mnemonic Operands ADL Mode Cycles Op Codes<br />

JP cc,mn 0 4 kk, mn, mn<br />

JP cc,Mmn 1 5 kk, mn, mn, MM<br />

JP.SS cc,mn X 5 40, kk, mn, mn<br />

JP.LIL cc,Mmn X 6 5B, kk, mn, mn, MM<br />

kk = binary code 11 ccc 010 where ccc identifies one of status conditions<br />

assembled as follows into the object code.<br />

ccc Condition Relevant Flag<br />

000 NZ (non-zero) Z<br />

001 Z (zero) Z<br />

010 NC (non-carry) C<br />

011 C (carry) C<br />

100 PO (parity odd) P/V<br />

101 PE (parity even) P/V<br />

110 P (sign positive) S<br />

111 M (sign negative) s<br />

UM007701-1100