Soft-Core Processor Design - CiteSeer

Soft-Core Processor Design - CiteSeer

Soft-Core Processor Design - CiteSeer

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

�¦��¥���¥<br />

� �§¥�¨��<br />

��§©�¦£ �<br />

§ ¨��©¥�¨��<br />

� ���<br />

�����<br />

� � ¢<br />

����¢<br />

�����<br />

����¢<br />

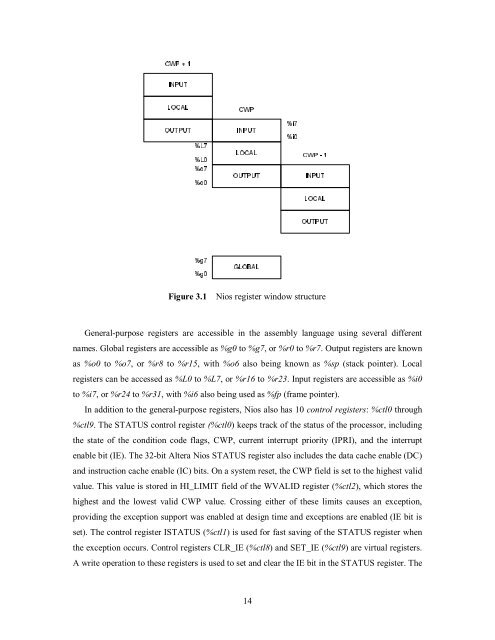

General-purpose registers are accessible in the assembly language using several different<br />

names. Global registers are accessible as %g0 to %g7, or %r0 to %r7. Output registers are known<br />

as %o0 to %o7, or %r8 to %r15, with %o6 also being known as %sp (stack pointer). Local<br />

registers can be accessed as %L0 to %L7, or %r16 to %r23. Input registers are accessible as %i0<br />

to %i7, or %r24 to %r31, with %i6 also being used as %fp (frame pointer).<br />

�¦��¥<br />

� �§¥�¨��<br />

��§©�¨£©�<br />

§ ¨��¦¥�¨��<br />

��§¢¡¤£©�<br />

In addition to the general-purpose registers, Nios also has 10 control registers: %ctl0 through<br />

%ctl9. The STATUS control register (%ctl0) keeps track of the status of the processor, including<br />

the state of the condition code flags, CWP, current interrupt priority (IPRI), and the interrupt<br />

enable bit (IE). The 32-bit Altera Nios STATUS register also includes the data cache enable (DC)<br />

and instruction cache enable (IC) bits. On a system reset, the CWP field is set to the highest valid<br />

value. This value is stored in HI_LIMIT field of the WVALID register (%ctl2), which stores the<br />

highest and the lowest valid CWP value. Crossing either of these limits causes an exception,<br />

providing the exception support was enabled at design time and exceptions are enabled (IE bit is<br />

set). The control register ISTATUS (%ctl1) is used for fast saving of the STATUS register when<br />

the exception occurs. Control registers CLR_IE (%ctl8) and SET_IE (%ctl9) are virtual registers.<br />

A write operation to these registers is used to set and clear the IE bit in the STATUS register. The<br />

14<br />

��� �<br />

��� ¢<br />

�¦��¥���¥<br />

� �§¥�¨��<br />

��§ �¦£©�<br />

§ ¨��¦¥�¨��<br />

Figure 3.1 Nios register window structure