Soft-Core Processor Design - CiteSeer

Soft-Core Processor Design - CiteSeer

Soft-Core Processor Design - CiteSeer

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

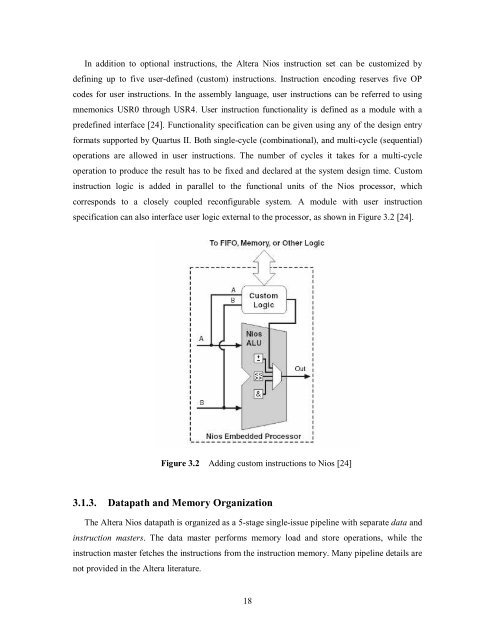

In addition to optional instructions, the Altera Nios instruction set can be customized by<br />

defining up to five user-defined (custom) instructions. Instruction encoding reserves five OP<br />

codes for user instructions. In the assembly language, user instructions can be referred to using<br />

mnemonics USR0 through USR4. User instruction functionality is defined as a module with a<br />

predefined interface [24]. Functionality specification can be given using any of the design entry<br />

formats supported by Quartus II. Both single-cycle (combinational), and multi-cycle (sequential)<br />

operations are allowed in user instructions. The number of cycles it takes for a multi-cycle<br />

operation to produce the result has to be fixed and declared at the system design time. Custom<br />

instruction logic is added in parallel to the functional units of the Nios processor, which<br />

corresponds to a closely coupled reconfigurable system. A module with user instruction<br />

specification can also interface user logic external to the processor, as shown in Figure 3.2 [24].<br />

3.1.3. Datapath and Memory Organization<br />

The Altera Nios datapath is organized as a 5-stage single-issue pipeline with separate data and<br />

instruction masters. The data master performs memory load and store operations, while the<br />

instruction master fetches the instructions from the instruction memory. Many pipeline details are<br />

not provided in the Altera literature.<br />

Figure 3.2 Adding custom instructions to Nios [24]<br />

18