Soft-Core Processor Design - CiteSeer

Soft-Core Processor Design - CiteSeer

Soft-Core Processor Design - CiteSeer

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Total # of Memory Accesses Performed by the CWP Manager<br />

8000<br />

7000<br />

6000<br />

5000<br />

4000<br />

3000<br />

2000<br />

1000<br />

0<br />

1 2 3 4 5 6 7 8 9 10 11 12<br />

Number of Register Windows Available to the Program<br />

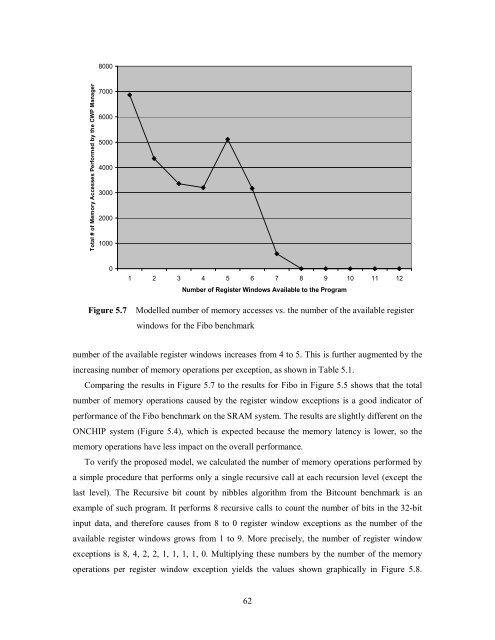

Figure 5.7 Modelled number of memory accesses vs. the number of the available register<br />

windows for the Fibo benchmark<br />

number of the available register windows increases from 4 to 5. This is further augmented by the<br />

increasing number of memory operations per exception, as shown in Table 5.1.<br />

Comparing the results in Figure 5.7 to the results for Fibo in Figure 5.5 shows that the total<br />

number of memory operations caused by the register window exceptions is a good indicator of<br />

performance of the Fibo benchmark on the SRAM system. The results are slightly different on the<br />

ONCHIP system (Figure 5.4), which is expected because the memory latency is lower, so the<br />

memory operations have less impact on the overall performance.<br />

To verify the proposed model, we calculated the number of memory operations performed by<br />

a simple procedure that performs only a single recursive call at each recursion level (except the<br />

last level). The Recursive bit count by nibbles algorithm from the Bitcount benchmark is an<br />

example of such program. It performs 8 recursive calls to count the number of bits in the 32-bit<br />

input data, and therefore causes from 8 to 0 register window exceptions as the number of the<br />

available register windows grows from 1 to 9. More precisely, the number of register window<br />

exceptions is 8, 4, 2, 2, 1, 1, 1, 1, 0. Multiplying these numbers by the number of the memory<br />

operations per register window exception yields the values shown graphically in Figure 5.8.<br />

62