Soft-Core Processor Design - CiteSeer

Soft-Core Processor Design - CiteSeer

Soft-Core Processor Design - CiteSeer

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Figure 5.1 shows that the performance of the ONCHIP system is the best for all benchmarks<br />

when the FIFO buffer has a unit size. The performance drop with the increasing buffer size<br />

results from the memory access conflicts, because both data and instructions reside in the same<br />

memory. If both instruction and data master request the memory access at the same time, the bus<br />

arbitration logic grants the access to one of the masters, while wait states are generated for the<br />

other. This is obvious from Figure 5.1, which shows that the Memory test benchmark suffers the<br />

biggest performance penalty because of the increasing FIFO buffer size. The Pipeline-Memory<br />

benchmark, which reads the data from the BOOT memory that is not accessed by the instruction<br />

master while the program is running, does not suffer any performance penalty. At the same time,<br />

the Pipeline-Memory benchmark that reads the data from the PROGRAM memory, suffers mildly<br />

from increasing the FIFO buffer size.<br />

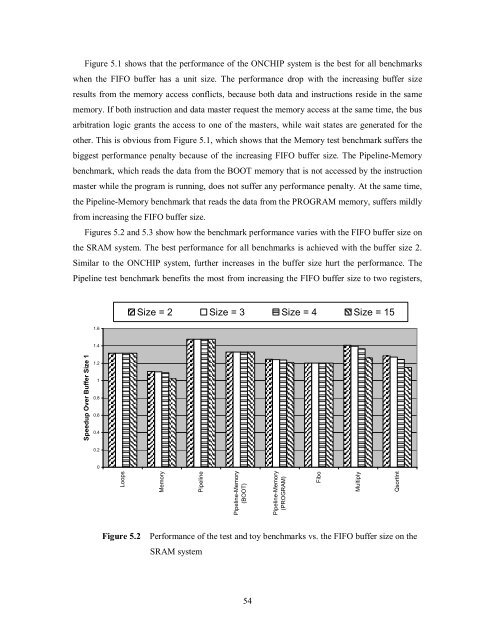

Figures 5.2 and 5.3 show how the benchmark performance varies with the FIFO buffer size on<br />

the SRAM system. The best performance for all benchmarks is achieved with the buffer size 2.<br />

Similar to the ONCHIP system, further increases in the buffer size hurt the performance. The<br />

Pipeline test benchmark benefits the most from increasing the FIFO buffer size to two registers,<br />

Speedup Over Buffer Size 1<br />

1.6<br />

1.4<br />

1.2<br />

1<br />

0.8<br />

0.6<br />

0.4<br />

0.2<br />

0<br />

Loops<br />

Size = 2 Size = 3 Size = 4 Size = 15<br />

Memory<br />

Pipeline<br />

Pipeline-Memory<br />

(BOOT)<br />

Figure 5.2 Performance of the test and toy benchmarks vs. the FIFO buffer size on the<br />

SRAM system<br />

54<br />

Pipeline-Memory<br />

(PROGRAM)<br />

Fibo<br />

Multiply<br />

QsortInt