Soft-Core Processor Design - CiteSeer

Soft-Core Processor Design - CiteSeer

Soft-Core Processor Design - CiteSeer

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

the logic resources may be more critical, so the noncritical resource may be used to implement<br />

the instruction decoder.<br />

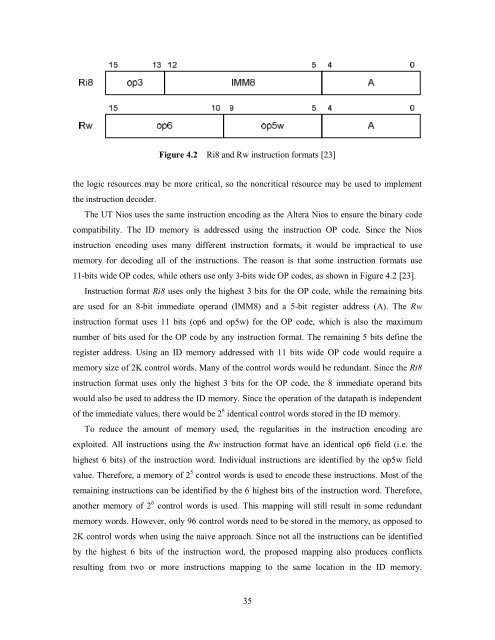

Figure 4.2 Ri8 and Rw instruction formats [23]<br />

The UT Nios uses the same instruction encoding as the Altera Nios to ensure the binary code<br />

compatibility. The ID memory is addressed using the instruction OP code. Since the Nios<br />

instruction encoding uses many different instruction formats, it would be impractical to use<br />

memory for decoding all of the instructions. The reason is that some instruction formats use<br />

11-bits wide OP codes, while others use only 3-bits wide OP codes, as shown in Figure 4.2 [23].<br />

Instruction format Ri8 uses only the highest 3 bits for the OP code, while the remaining bits<br />

are used for an 8-bit immediate operand (IMM8) and a 5-bit register address (A). The Rw<br />

instruction format uses 11 bits (op6 and op5w) for the OP code, which is also the maximum<br />

number of bits used for the OP code by any instruction format. The remaining 5 bits define the<br />

register address. Using an ID memory addressed with 11 bits wide OP code would require a<br />

memory size of 2K control words. Many of the control words would be redundant. Since the Ri8<br />

instruction format uses only the highest 3 bits for the OP code, the 8 immediate operand bits<br />

would also be used to address the ID memory. Since the operation of the datapath is independent<br />

of the immediate values, there would be 2 8 identical control words stored in the ID memory.<br />

To reduce the amount of memory used, the regularities in the instruction encoding are<br />

exploited. All instructions using the Rw instruction format have an identical op6 field (i.e. the<br />

highest 6 bits) of the instruction word. Individual instructions are identified by the op5w field<br />

value. Therefore, a memory of 2 5 control words is used to encode these instructions. Most of the<br />

remaining instructions can be identified by the 6 highest bits of the instruction word. Therefore,<br />

another memory of 2 6 control words is used. This mapping will still result in some redundant<br />

memory words. However, only 96 control words need to be stored in the memory, as opposed to<br />

2K control words when using the naive approach. Since not all the instructions can be identified<br />

by the highest 6 bits of the instruction word, the proposed mapping also produces conflicts<br />

resulting from two or more instructions mapping to the same location in the ID memory.<br />

35