Soft-Core Processor Design - CiteSeer

Soft-Core Processor Design - CiteSeer

Soft-Core Processor Design - CiteSeer

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Recursion<br />

Level<br />

# of recursive<br />

calls<br />

# of reg.<br />

windows<br />

available<br />

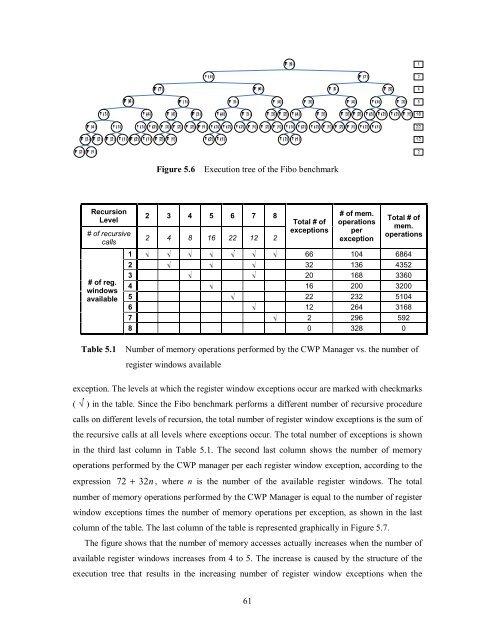

Figure 5.6 Execution tree of the Fibo benchmark<br />

2 3 4 5 6 7 8<br />

2 4 8 16 22 12 2<br />

exception. The levels at which the register window exceptions occur are marked with checkmarks<br />

( ) in the table. Since the Fibo benchmark performs a different number of recursive procedure<br />

calls on different levels of recursion, the total number of register window exceptions is the sum of<br />

the recursive calls at all levels where exceptions occur. The total number of exceptions is shown<br />

in the third last column in Table 5.1. The second last column shows the number of memory<br />

operations performed by the CWP manager per each register window exception, according to the<br />

expression 72 + 32n<br />

, where n is the number of the available register windows. The total<br />

number of memory operations performed by the CWP Manager is equal to the number of register<br />

window exceptions times the number of memory operations per exception, as shown in the last<br />

column of the table. The last column of the table is represented graphically in Figure 5.7.<br />

The figure shows that the number of memory accesses actually increases when the number of<br />

available register windows increases from 4 to 5. The increase is caused by the structure of the<br />

execution tree that results in the increasing number of register window exceptions when the<br />

61<br />

Total # of<br />

exceptions<br />

# of mem.<br />

operations<br />

per<br />

exception<br />

Total # of<br />

mem.<br />

operations<br />

¡ ¡ ¡ ¡ ¡ ¡ ¡<br />

¡ ¡ ¡<br />

¡ ¡<br />

¡<br />

¡<br />

¡<br />

¡<br />

1 66 104 6864<br />

2 32 136 4352<br />

3 20 168 3360<br />

4 16 200 3200<br />

5 22 232 5104<br />

6 12 264 3168<br />

7 2 296 592<br />

8 0 328 0<br />

Table 5.1 Number of memory operations performed by the CWP Manager vs. the number of<br />

register windows available