Diplom Informatik(FH) - FHInfo - Fachhochschule Kaiserslautern

Diplom Informatik(FH) - FHInfo - Fachhochschule Kaiserslautern

Diplom Informatik(FH) - FHInfo - Fachhochschule Kaiserslautern

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Modulhandbuch - Angewandte <strong>Informatik</strong> (AI04) - <strong>Diplom</strong> <strong>Informatik</strong>(<strong>FH</strong>)<br />

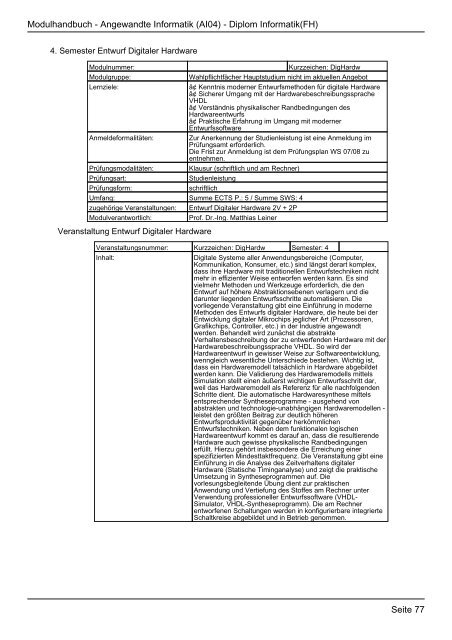

4. Semester Entwurf Digitaler Hardware<br />

Modulnummer: Kurzzeichen: DigHardw<br />

Modulgruppe: Wahlpflichtfächer Hauptstudium nicht im aktuellen Angebot<br />

Lernziele: ⢠Kenntnis moderner Entwurfsmethoden für digitale Hardware<br />

⢠Sicherer Umgang mit der Hardwarebeschreibungssprache<br />

VHDL<br />

⢠Verständnis physikalischer Randbedingungen des<br />

Hardwareentwurfs<br />

⢠Praktische Erfahrung im Umgang mit moderner<br />

Entwurfssoftware<br />

Anmeldeformalitäten: Zur Anerkennung der Studienleistung ist eine Anmeldung im<br />

Prüfungsamt erforderlich.<br />

Die Frist zur Anmeldung ist dem Prüfungsplan WS 07/08 zu<br />

entnehmen.<br />

Prüfungsmodalitäten: Klausur (schriftlich und am Rechner)<br />

Prüfungsart: Studienleistung<br />

Prüfungsform: schriftlich<br />

Umfang: Summe ECTS P.: 5 / Summe SWS: 4<br />

zugehörige Veranstaltungen: Entwurf Digitaler Hardware 2V + 2P<br />

Modulverantwortlich: Prof. Dr.-Ing. Matthias Leiner<br />

Veranstaltung Entwurf Digitaler Hardware<br />

Veranstaltungsnummer: Kurzzeichen: DigHardw Semester: 4<br />

Inhalt: Digitale Systeme aller Anwendungsbereiche (Computer,<br />

Kommunikation, Konsumer, etc.) sind längst derart komplex,<br />

dass ihre Hardware mit traditionellen Entwurfstechniken nicht<br />

mehr in effizienter Weise entworfen werden kann. Es sind<br />

vielmehr Methoden und Werkzeuge erforderlich, die den<br />

Entwurf auf höhere Abstraktionsebenen verlagern und die<br />

darunter liegenden Entwurfsschritte automatisieren. Die<br />

vorliegende Veranstaltung gibt eine Einführung in moderne<br />

Methoden des Entwurfs digitaler Hardware, die heute bei der<br />

Entwicklung digitaler Mikrochips jeglicher Art (Prozessoren,<br />

Grafikchips, Controller, etc.) in der Industrie angewandt<br />

werden. Behandelt wird zunächst die abstrakte<br />

Verhaltensbeschreibung der zu entwerfenden Hardware mit der<br />

Hardwarebeschreibungssprache VHDL. So wird der<br />

Hardwareentwurf in gewisser Weise zur Softwareentwicklung,<br />

wenngleich wesentliche Unterschiede bestehen. Wichtig ist,<br />

dass ein Hardwaremodell tatsächlich in Hardware abgebildet<br />

werden kann. Die Validierung des Hardwaremodells mittels<br />

Simulation stellt einen äußerst wichtigen Entwurfsschritt dar,<br />

weil das Hardwaremodell als Referenz für alle nachfolgenden<br />

Schritte dient. Die automatische Hardwaresynthese mittels<br />

entsprechender Syntheseprogramme - ausgehend von<br />

abstrakten und technologie-unabhängigen Hardwaremodellen -<br />

leistet den größten Beitrag zur deutlich höheren<br />

Entwurfsproduktivität gegenüber herkömmlichen<br />

Entwurfstechniken. Neben dem funktionalen logischen<br />

Hardwareentwurf kommt es darauf an, dass die resultierende<br />

Hardware auch gewisse physikalische Randbedingungen<br />

erfüllt. Hierzu gehört insbesondere die Erreichung einer<br />

spezifizierten Mindesttaktfrequenz. Die Veranstaltung gibt eine<br />

Einführung in die Analyse des Zeitverhaltens digitaler<br />

Hardware (Statische Timinganalyse) und zeigt die praktische<br />

Umsetzung in Syntheseprogrammen auf. Die<br />

vorlesungsbegleitende Übung dient zur praktischen<br />

Anwendung und Vertiefung des Stoffes am Rechner unter<br />

Verwendung professioneller Entwurfssoftware (VHDL-<br />

Simulator, VHDL-Syntheseprogramm). Die am Rechner<br />

entworfenen Schaltungen werden in konfigurierbare integrierte<br />

Schaltkreise abgebildet und in Betrieb genommen.<br />

Seite 77