Preliminary C8051F120/1/2/3 C8051F124/5/6/7 - KEMT FEI TUKE

Preliminary C8051F120/1/2/3 C8051F124/5/6/7 - KEMT FEI TUKE

Preliminary C8051F120/1/2/3 C8051F124/5/6/7 - KEMT FEI TUKE

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

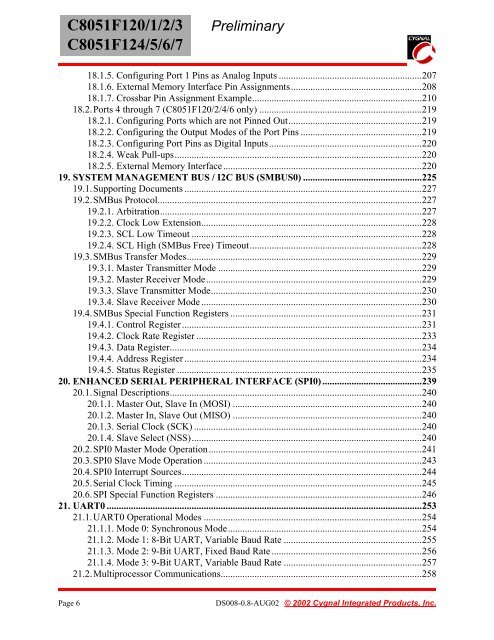

<strong>C8051F120</strong>/1/2/3<br />

<strong>C8051F124</strong>/5/6/7<br />

<strong>Preliminary</strong><br />

18.1.5. Configuring Port 1 Pins as Analog Inputs ...........................................................207<br />

18.1.6. External Memory Interface Pin Assignments......................................................208<br />

18.1.7. Crossbar Pin Assignment Example......................................................................210<br />

18.2.Ports 4 through 7 (<strong>C8051F120</strong>/2/4/6 only) ...................................................................219<br />

18.2.1. Configuring Ports which are not Pinned Out.......................................................219<br />

18.2.2. Configuring the Output Modes of the Port Pins ..................................................219<br />

18.2.3. Configuring Port Pins as Digital Inputs...............................................................220<br />

18.2.4. Weak Pull-ups......................................................................................................220<br />

18.2.5. External Memory Interface..................................................................................220<br />

19. SYSTEM MANAGEMENT BUS / I2C BUS (SMBUS0) .................................................225<br />

19.1.Supporting Documents ..................................................................................................227<br />

19.2.SMBus Protocol.............................................................................................................227<br />

19.2.1. Arbitration............................................................................................................227<br />

19.2.2. Clock Low Extension...........................................................................................228<br />

19.2.3. SCL Low Timeout ...............................................................................................228<br />

19.2.4. SCL High (SMBus Free) Timeout.......................................................................228<br />

19.3.SMBus Transfer Modes.................................................................................................229<br />

19.3.1. Master Transmitter Mode ....................................................................................229<br />

19.3.2. Master Receiver Mode.........................................................................................229<br />

19.3.3. Slave Transmitter Mode.......................................................................................230<br />

19.3.4. Slave Receiver Mode ...........................................................................................230<br />

19.4.SMBus Special Function Registers ...............................................................................231<br />

19.4.1. Control Register...................................................................................................231<br />

19.4.2. Clock Rate Register .............................................................................................233<br />

19.4.3. Data Register........................................................................................................234<br />

19.4.4. Address Register ..................................................................................................234<br />

19.4.5. Status Register .....................................................................................................235<br />

20. ENHANCED SERIAL PERIPHERAL INTERFACE (SPI0) .........................................239<br />

20.1.Signal Descriptions........................................................................................................240<br />

20.1.1. Master Out, Slave In (MOSI) ..............................................................................240<br />

20.1.2. Master In, Slave Out (MISO) ..............................................................................240<br />

20.1.3. Serial Clock (SCK) ..............................................................................................240<br />

20.1.4. Slave Select (NSS)...............................................................................................240<br />

20.2.SPI0 Master Mode Operation........................................................................................241<br />

20.3.SPI0 Slave Mode Operation ..........................................................................................243<br />

20.4.SPI0 Interrupt Sources...................................................................................................244<br />

20.5.Serial Clock Timing ......................................................................................................245<br />

20.6.SPISpecial Function Registers .....................................................................................246<br />

21. UART0 ..................................................................................................................................253<br />

21.1.UART0 Operational Modes ..........................................................................................254<br />

21.1.1. Mode 0: Synchronous Mode................................................................................254<br />

21.1.2. Mode 1: 8-Bit UART, Variable Baud Rate .........................................................255<br />

21.1.3. Mode 2: 9-Bit UART, Fixed Baud Rate ..............................................................256<br />

21.1.4. Mode 3: 9-Bit UART, Variable Baud Rate .........................................................257<br />

21.2.Multiprocessor Communications...................................................................................258<br />

Page 6<br />

DS008-0.8-AUG02 © 2002 Cygnal Integrated Products, Inc.