PPKE ITK PhD and MPhil Thesis Classes

PPKE ITK PhD and MPhil Thesis Classes

PPKE ITK PhD and MPhil Thesis Classes

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

1.4 Field Programmable Gate Arrays 13<br />

containing on-chip memory blocks <strong>and</strong> DSP blocks (dedicated multipliers, <strong>and</strong><br />

multiply/accumulator units).<br />

Despite the fact that there are many FPGA families, the reconfigurable computers<br />

are exclusively SRAM programmable devices. That means, the configuration<br />

of the FPGA, the code as a generated ’bitfile’ – which defines the device<br />

implemented algorithm – stored in an on-chip SRAM. With the loading of the<br />

configurations into the SRAM memory different algorithms can be executed efficiently.<br />

The configuration defines the logic function, which is computed by the<br />

logic blocks <strong>and</strong> the interconnection-pattern.<br />

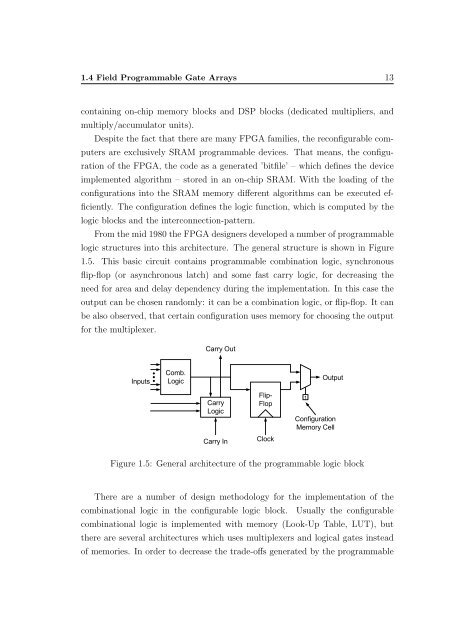

From the mid 1980 the FPGA designers developed a number of programmable<br />

logic structures into this architecture. The general structure is shown in Figure<br />

1.5. This basic circuit contains programmable combination logic, synchronous<br />

flip-flop (or asynchronous latch) <strong>and</strong> some fast carry logic, for decreasing the<br />

need for area <strong>and</strong> delay dependency during the implementation. In this case the<br />

output can be chosen r<strong>and</strong>omly: it can be a combination logic, or flip-flop. It can<br />

be also observed, that certain configuration uses memory for choosing the output<br />

for the multiplexer.<br />

Figure 1.5: General architecture of the programmable logic block<br />

There are a number of design methodology for the implementation of the<br />

combinational logic in the configurable logic block. Usually the configurable<br />

combinational logic is implemented with memory (Look-Up Table, LUT), but<br />

there are several architectures which uses multiplexers <strong>and</strong> logical gates instead<br />

of memories. In order to decrease the trade-offs generated by the programmable

![optika tervezés [Kompatibilitási mód] - Ez itt...](https://img.yumpu.com/45881475/1/190x146/optika-tervezacs-kompatibilitasi-mad-ez-itt.jpg?quality=85)