PPKE ITK PhD and MPhil Thesis Classes

PPKE ITK PhD and MPhil Thesis Classes

PPKE ITK PhD and MPhil Thesis Classes

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

1.4 Field Programmable Gate Arrays 17<br />

• to develop a more complex element using the elements of the clusters,<br />

• non-programmable wiring for transferring fast carry bits for avoiding the<br />

extra delays when programmable interconnections (routing) are used.<br />

There are three main implementations for the global routing (which are used<br />

by the Xilinx by their FPGA family): row-based, symmetric (isl<strong>and</strong>) type <strong>and</strong><br />

cellular architecture. Modern FPGA architectures are using significantly complex<br />

routing architectures, but their structures are based on these three.<br />

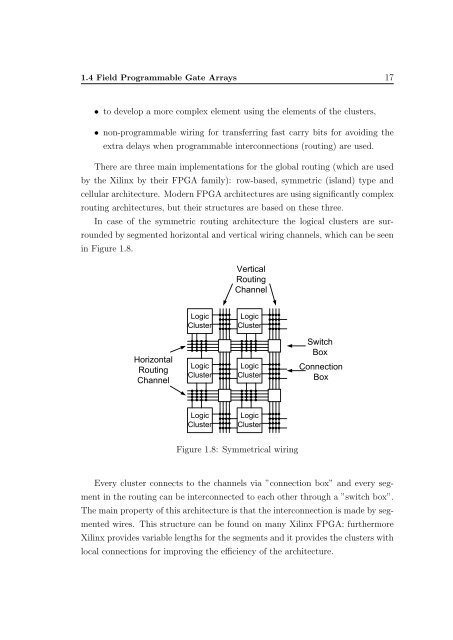

In case of the symmetric routing architecture the logical clusters are surrounded<br />

by segmented horizontal <strong>and</strong> vertical wiring channels, which can be seen<br />

in Figure 1.8.<br />

Figure 1.8: Symmetrical wiring<br />

Every cluster connects to the channels via ”connection box” <strong>and</strong> every segment<br />

in the routing can be interconnected to each other through a ”switch box”.<br />

The main property of this architecture is that the interconnection is made by segmented<br />

wires. This structure can be found on many Xilinx FPGA: furthermore<br />

Xilinx provides variable lengths for the segments <strong>and</strong> it provides the clusters with<br />

local connections for improving the efficiency of the architecture.

![optika tervezés [Kompatibilitási mód] - Ez itt...](https://img.yumpu.com/45881475/1/190x146/optika-tervezacs-kompatibilitasi-mad-ez-itt.jpg?quality=85)