Download Full Issue in PDF - Academy Publisher

Download Full Issue in PDF - Academy Publisher

Download Full Issue in PDF - Academy Publisher

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

JOURNAL OF COMPUTERS, VOL. 8, NO. 6, JUNE 2013 1409<br />

Algorithm 1: Two stage Simulated Anneal<strong>in</strong>g<br />

Inputs: Temperature coefficient α<br />

Number of state variables N<br />

Exit temperature T 0<br />

Temperature threshold T threshold<br />

Outputs: The best solution S best<br />

beg<strong>in</strong><br />

<strong>in</strong>itialise a solution S current and temperature T<br />

while (T < T 0 ) { // outer loop<br />

k = 0<br />

while (k < N 3 ) { // <strong>in</strong>ner loop<br />

if (T > T threshold ) S new = generate solution via<br />

exchange method<br />

else<br />

S new = generate solution via swap methods<br />

k= k + 1<br />

r = random (0, 1)<br />

∆C = cost (S new ) – cost (S current )<br />

if (r < exp (–∆C/T)) {<br />

S current = S new<br />

if (cost (S best ) > cost (S current ))<br />

S best = S current<br />

}<br />

} // end of <strong>in</strong>ner loop<br />

T =αT<br />

} // end of outer loop<br />

Output the best solution S best<br />

IV. EXPERIMENTAL RESULTS<br />

The algorithm has been implemented <strong>in</strong> C++ and the<br />

results have been obta<strong>in</strong>ed on a personal computer with<br />

an INTEL CPU 2.4 GHz and 4 GB RAM. A Gaussian<br />

elim<strong>in</strong>ation method is used to f<strong>in</strong>d the total transition<br />

probabilities accord<strong>in</strong>g to the STT of an FSM.<br />

ESSPRESSO is used to m<strong>in</strong>imise the circuit for each state<br />

assignment. The product terms from this m<strong>in</strong>imisation<br />

determ<strong>in</strong>e the number of cubes for that assignment.<br />

Switch<strong>in</strong>g activity is calculated by (6). T, T threshold and T 0<br />

are set to 10000, 100 and 0.1, respectively. In order to<br />

balance the required solution quality and computational<br />

time, temperature schedule coefficient α is selected to<br />

0.95 and 0.8 <strong>in</strong> the rough anneal<strong>in</strong>g stage and focus<strong>in</strong>g<br />

anneal<strong>in</strong>g stage, respectively. Based on the numerous<br />

experimental results, when γ is 0.3, it performs the best<br />

trade-off between area and power consumption.<br />

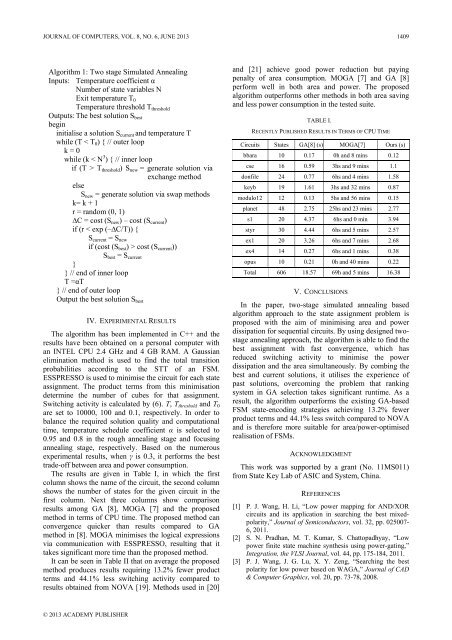

The results are given <strong>in</strong> Table I, <strong>in</strong> which the first<br />

column shows the name of the circuit, the second column<br />

shows the number of states for the given circuit <strong>in</strong> the<br />

first column. Next three columns show comparison<br />

results among GA [8], MOGA [7] and the proposed<br />

method <strong>in</strong> terms of CPU time. The proposed method can<br />

convergence quicker than results compared to GA<br />

method <strong>in</strong> [8]. MOGA m<strong>in</strong>imises the logical expressions<br />

via communication with ESSPRESSO, result<strong>in</strong>g that it<br />

takes significant more time than the proposed method.<br />

It can be seen <strong>in</strong> Table II that on average the proposed<br />

method produces results requir<strong>in</strong>g 13.2% fewer product<br />

terms and 44.1% less switch<strong>in</strong>g activity compared to<br />

results obta<strong>in</strong>ed from NOVA [19]. Methods used <strong>in</strong> [20]<br />

and [21] achieve good power reduction but pay<strong>in</strong>g<br />

penalty of area consumption. MOGA [7] and GA [8]<br />

perform well <strong>in</strong> both area and power. The proposed<br />

algorithm outperforms other methods <strong>in</strong> both area sav<strong>in</strong>g<br />

and less power consumption <strong>in</strong> the tested suite.<br />

TABLE I.<br />

RECENTLY PUBLISHED RESULTS IN TERMS OF CPU TIME<br />

Circuits States GA[8] (s) MOGA[7] Ours (s)<br />

bbara 10 0.17 0h and 8 m<strong>in</strong>s 0.12<br />

cse 16 0.59 3hs and 9 m<strong>in</strong>s 1.1<br />

donfile 24 0.77 6hs and 4 m<strong>in</strong>s 1.58<br />

keyb 19 1.61 3hs and 32 m<strong>in</strong>s 0.87<br />

modulo12 12 0.13 5hs and 56 m<strong>in</strong>s 0.15<br />

planet 48 2.75 25hs and 23 m<strong>in</strong>s 2.77<br />

s1 20 4.37 6hs and 0 m<strong>in</strong> 3.94<br />

styr 30 4.44 6hs and 5 m<strong>in</strong>s 2.57<br />

ex1 20 3.26 6hs and 7 m<strong>in</strong>s 2.68<br />

ex4 14 0.27 6hs and 1 m<strong>in</strong>s 0.38<br />

opus 10 0.21 0h and 40 m<strong>in</strong>s 0.22<br />

Total 606 18.57 69h and 5 m<strong>in</strong>s 16.38<br />

V. CONCLUSIONS<br />

In the paper, two-stage simulated anneal<strong>in</strong>g based<br />

algorithm approach to the state assignment problem is<br />

proposed with the aim of m<strong>in</strong>imis<strong>in</strong>g area and power<br />

dissipation for sequential circuits. By us<strong>in</strong>g designed twostage<br />

anneal<strong>in</strong>g approach, the algorithm is able to f<strong>in</strong>d the<br />

best assignment with fast convergence, which has<br />

reduced switch<strong>in</strong>g activity to m<strong>in</strong>imise the power<br />

dissipation and the area simultaneously. By comb<strong>in</strong>g the<br />

best and current solutions, it utilises the experience of<br />

past solutions, overcom<strong>in</strong>g the problem that rank<strong>in</strong>g<br />

system <strong>in</strong> GA selection takes significant runtime. As a<br />

result, the algorithm outperforms the exist<strong>in</strong>g GA-based<br />

FSM state-encod<strong>in</strong>g strategies achiev<strong>in</strong>g 13.2% fewer<br />

product terms and 44.1% less switch compared to NOVA<br />

and is therefore more suitable for area/power-optimised<br />

realisation of FSMs.<br />

ACKNOWLEDGMENT<br />

This work was supported by a grant (No. 11MS011)<br />

from State Key Lab of ASIC and System, Ch<strong>in</strong>a.<br />

REFERENCES<br />

[1] P. J. Wang, H. Li, “Low power mapp<strong>in</strong>g for AND/XOR<br />

circuits and its application <strong>in</strong> search<strong>in</strong>g the best mixedpolarity,”<br />

Journal of Semiconductors, vol. 32, pp. 025007-<br />

6, 2011.<br />

[2] S. N. Pradhan, M. T. Kumar, S. Chattopadhyay, “Low<br />

power f<strong>in</strong>ite state mach<strong>in</strong>e synthesis us<strong>in</strong>g power-gat<strong>in</strong>g,”<br />

Integration, the VLSI Journal, vol. 44, pp. 175-184, 2011.<br />

[3] P. J. Wang, J. G. Lu, X. Y. Zeng, “Search<strong>in</strong>g the best<br />

polarity for low power based on WAGA,” Journal of CAD<br />

& Computer Graphics, vol. 20, pp. 73-78, 2008.<br />

© 2013 ACADEMY PUBLISHER