Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Philips Semiconductors Preliminary <strong>User</strong> <strong>Manual</strong><br />

ARM-based Microcontroller<br />

<strong>LPC2131</strong>/<strong>2132</strong>/<strong>2138</strong><br />

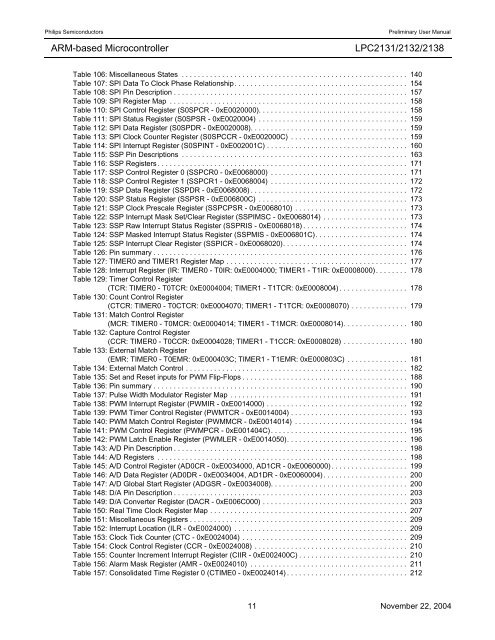

Table 106: Miscellaneous States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140<br />

Table 107: SPI Data To Clock Phase Relationship. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154<br />

Table 108: SPI Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157<br />

Table 109: SPI Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158<br />

Table 110: SPI Control Register (S0SPCR - 0xE0020000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158<br />

Table 111: SPI Status Register (S0SPSR - 0xE0020004) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159<br />

Table 112: SPI Data Register (S0SPDR - 0xE0020008). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159<br />

Table 113: SPI Clock Counter Register (S0SPCCR - 0xE002000C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159<br />

Table 114: SPI Interrupt Register (S0SPINT - 0xE002001C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160<br />

Table 115: SSP Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163<br />

Table 116: SSP Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171<br />

Table 117: SSP Control Register 0 (SSPCR0 - 0xE0068000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171<br />

Table 118: SSP Control Register 1 (SSPCR1 - 0xE0068004) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172<br />

Table 119: SSP Data Register (SSPDR - 0xE0068008) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172<br />

Table 120: SSP Status Register (SSPSR - 0xE006800C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173<br />

Table 121: SSP Clock Prescale Register (SSPCPSR - 0xE0068010) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173<br />

Table 122: SSP Interrupt Mask Set/Clear Register (SSPIMSC - 0xE0068014) . . . . . . . . . . . . . . . . . . . . . 173<br />

Table 123: SSP Raw Interrupt Status Register (SSPRIS - 0xE0068018) . . . . . . . . . . . . . . . . . . . . . . . . . . 174<br />

Table 124: SSP Masked Interrupt Status Register (SSPMIS - 0xE006801C). . . . . . . . . . . . . . . . . . . . . . . 174<br />

Table 125: SSP Interrupt Clear Register (SSPICR - 0xE0068020). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174<br />

Table 126: Pin summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176<br />

Table 127: TIMER0 and TIMER1 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177<br />

Table 128: Interrupt Register (IR: TIMER0 - T0IR: 0xE0004000; TIMER1 - T1IR: 0xE0008000). . . . . . . . 178<br />

Table 129: Timer Control Register<br />

(TCR: TIMER0 - T0TCR: 0xE0004004; TIMER1 - T1TCR: 0xE0008004) . . . . . . . . . . . . . . . . . 178<br />

Table 130: Count Control Register<br />

(CTCR: TIMER0 - T0CTCR: 0xE0004070; TIMER1 - T1TCR: 0xE0008070) . . . . . . . . . . . . . . 179<br />

Table 131: Match Control Register<br />

(MCR: TIMER0 - T0MCR: 0xE0004014; TIMER1 - T1MCR: 0xE0008014). . . . . . . . . . . . . . . . 180<br />

Table 132: Capture Control Register<br />

(CCR: TIMER0 - T0CCR: 0xE0004028; TIMER1 - T1CCR: 0xE0008028) . . . . . . . . . . . . . . . . 180<br />

Table 133: External Match Register<br />

(EMR: TIMER0 - T0EMR: 0xE000403C; TIMER1 - T1EMR: 0xE000803C) . . . . . . . . . . . . . . . 181<br />

Table 134: External Match Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182<br />

Table 135: Set and Reset inputs for PWM Flip-Flops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188<br />

Table 136: Pin summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190<br />

Table 137: Pulse Width Modulator Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191<br />

Table 138: PWM Interrupt Register (PWMIR - 0xE0014000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192<br />

Table 139: PWM Timer Control Register (PWMTCR - 0xE0014004) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193<br />

Table 140: PWM Match Control Register (PWMMCR - 0xE0014014) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194<br />

Table 141: PWM Control Register (PWMPCR - 0xE001404C). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195<br />

Table 142: PWM Latch Enable Register (PWMLER - 0xE0014050). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196<br />

Table 143: A/D Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198<br />

Table 144: A/D Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198<br />

Table 145: A/D Control Register (AD0CR - 0xE0034000, AD1CR - 0xE0060000). . . . . . . . . . . . . . . . . . . 199<br />

Table 146: A/D Data Register (AD0DR - 0xE0034004, AD1DR - 0xE0060004). . . . . . . . . . . . . . . . . . . . . 200<br />

Table 147: A/D Global Start Register (ADGSR - 0xE0034008). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200<br />

Table 148: D/A Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203<br />

Table 149: D/A Converter Register (DACR - 0xE006C000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203<br />

Table 150: Real Time Clock Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207<br />

Table 151: Miscellaneous Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209<br />

Table 152: Interrupt Location (ILR - 0xE0024000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209<br />

Table 153: Clock Tick Counter (CTC - 0xE0024004) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209<br />

Table 154: Clock Control Register (CCR - 0xE0024008) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210<br />

Table 155: Counter Increment Interrupt Register (CIIR - 0xE002400C) . . . . . . . . . . . . . . . . . . . . . . . . . . . 210<br />

Table 156: Alarm Mask Register (AMR - 0xE0024010) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211<br />

Table 157: Consolidated Time Register 0 (CTIME0 - 0xE0024014) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212<br />

11 November 22, 2004