You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Philips Semiconductors Preliminary <strong>User</strong> <strong>Manual</strong><br />

ARM-based Microcontroller<br />

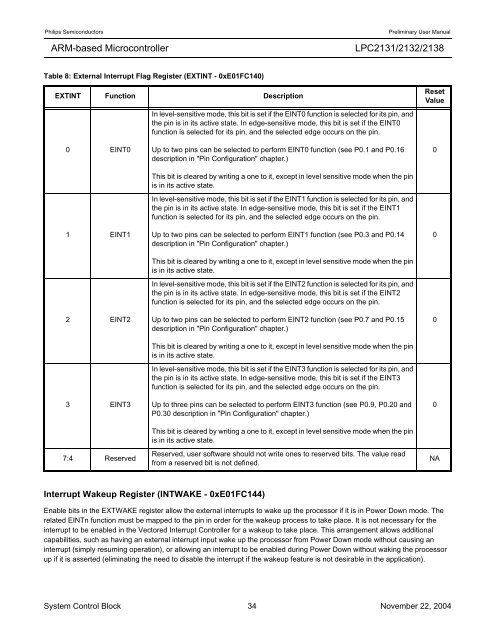

Table 8: External Interrupt Flag Register (EXTINT - 0xE01FC140)<br />

EXTINT Function Description<br />

0 EINT0<br />

1 EINT1<br />

2 EINT2<br />

3 EINT3<br />

7:4 Reserved<br />

Interrupt Wakeup Register (INTWAKE - 0xE01FC144)<br />

<strong>LPC2131</strong>/<strong>2132</strong>/<strong>2138</strong><br />

In level-sensitive mode, this bit is set if the EINT0 function is selected for its pin, and<br />

the pin is in its active state. In edge-sensitive mode, this bit is set if the EINT0<br />

function is selected for its pin, and the selected edge occurs on the pin.<br />

Up to two pins can be selected to perform EINT0 function (see P0.1 and P0.16<br />

description in "Pin Configuration" chapter.)<br />

This bit is cleared by writing a one to it, except in level sensitive mode when the pin<br />

is in its active state.<br />

In level-sensitive mode, this bit is set if the EINT1 function is selected for its pin, and<br />

the pin is in its active state. In edge-sensitive mode, this bit is set if the EINT1<br />

function is selected for its pin, and the selected edge occurs on the pin.<br />

Up to two pins can be selected to perform EINT1 function (see P0.3 and P0.14<br />

description in "Pin Configuration" chapter.)<br />

This bit is cleared by writing a one to it, except in level sensitive mode when the pin<br />

is in its active state.<br />

In level-sensitive mode, this bit is set if the EINT2 function is selected for its pin, and<br />

the pin is in its active state. In edge-sensitive mode, this bit is set if the EINT2<br />

function is selected for its pin, and the selected edge occurs on the pin.<br />

Up to two pins can be selected to perform EINT2 function (see P0.7 and P0.15<br />

description in "Pin Configuration" chapter.)<br />

This bit is cleared by writing a one to it, except in level sensitive mode when the pin<br />

is in its active state.<br />

In level-sensitive mode, this bit is set if the EINT3 function is selected for its pin, and<br />

the pin is in its active state. In edge-sensitive mode, this bit is set if the EINT3<br />

function is selected for its pin, and the selected edge occurs on the pin.<br />

Up to three pins can be selected to perform EINT3 function (see P0.9, P0.20 and<br />

P0.30 description in "Pin Configuration" chapter.)<br />

This bit is cleared by writing a one to it, except in level sensitive mode when the pin<br />

is in its active state.<br />

Reserved, user software should not write ones to reserved bits. The value read<br />

from a reserved bit is not defined.<br />

Reset<br />

Value<br />

Enable bits in the EXTWAKE register allow the external interrupts to wake up the processor if it is in Power Down mode. The<br />

related EINTn function must be mapped to the pin in order for the wakeup process to take place. It is not necessary for the<br />

interrupt to be enabled in the Vectored Interrupt Controller for a wakeup to take place. This arrangement allows additional<br />

capabilities, such as having an external interrupt input wake up the processor from Power Down mode without causing an<br />

interrupt (simply resuming operation), or allowing an interrupt to be enabled during Power Down without waking the processor<br />

up if it is asserted (eliminating the need to disable the interrupt if the wakeup feature is not desirable in the application).<br />

System Control Block 34 November 22, 2004<br />

0<br />

0<br />

0<br />

0<br />

NA