Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Philips Semiconductors Preliminary <strong>User</strong> <strong>Manual</strong><br />

ARM-based Microcontroller<br />

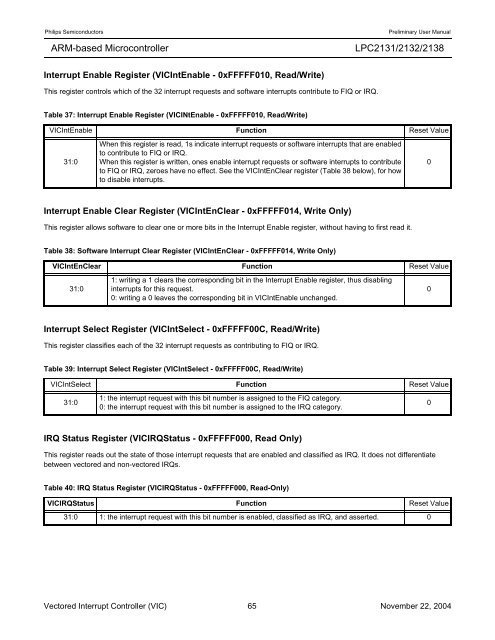

Interrupt Enable Register (VICIntEnable - 0xFFFFF010, Read/Write)<br />

This register controls which of the 32 interrupt requests and software interrupts contribute to FIQ or IRQ.<br />

Table 37: Interrupt Enable Register (VICINtEnable - 0xFFFFF010, Read/Write)<br />

Interrupt Enable Clear Register (VICIntEnClear - 0xFFFFF014, Write Only)<br />

<strong>LPC2131</strong>/<strong>2132</strong>/<strong>2138</strong><br />

VICIntEnable Function Reset Value<br />

31:0<br />

When this register is read, 1s indicate interrupt requests or software interrupts that are enabled<br />

to contribute to FIQ or IRQ.<br />

When this register is written, ones enable interrupt requests or software interrupts to contribute<br />

to FIQ or IRQ, zeroes have no effect. See the VICIntEnClear register (Table 38 below), for how<br />

to disable interrupts.<br />

This register allows software to clear one or more bits in the Interrupt Enable register, without having to first read it.<br />

Table 38: Software Interrupt Clear Register (VICIntEnClear - 0xFFFFF014, Write Only)<br />

VICIntEnClear Function Reset Value<br />

31:0<br />

1: writing a 1 clears the corresponding bit in the Interrupt Enable register, thus disabling<br />

interrupts for this request.<br />

0: writing a 0 leaves the corresponding bit in VICIntEnable unchanged.<br />

Interrupt Select Register (VICIntSelect - 0xFFFFF00C, Read/Write)<br />

This register classifies each of the 32 interrupt requests as contributing to FIQ or IRQ.<br />

Table 39: Interrupt Select Register (VICIntSelect - 0xFFFFF00C, Read/Write)<br />

VICIntSelect Function Reset Value<br />

31:0<br />

1: the interrupt request with this bit number is assigned to the FIQ category.<br />

0: the interrupt request with this bit number is assigned to the IRQ category.<br />

IRQ Status Register (VICIRQStatus - 0xFFFFF000, Read Only)<br />

This register reads out the state of those interrupt requests that are enabled and classified as IRQ. It does not differentiate<br />

between vectored and non-vectored IRQs.<br />

Table 40: IRQ Status Register (VICIRQStatus - 0xFFFFF000, Read-Only)<br />

VICIRQStatus Function Reset Value<br />

31:0 1: the interrupt request with this bit number is enabled, classified as IRQ, and asserted. 0<br />

Vectored Interrupt Controller (VIC) 65 November 22, 2004<br />

0<br />

0<br />

0