You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Philips Semiconductors Preliminary <strong>User</strong> <strong>Manual</strong><br />

ARM-based Microcontroller<br />

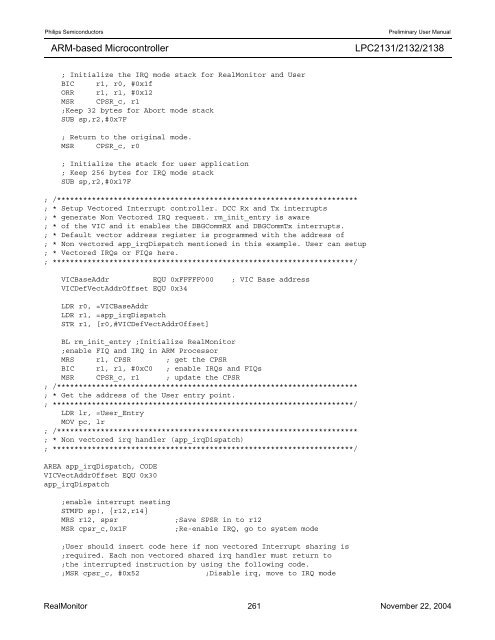

; Initialize the IRQ mode stack for RealMonitor and <strong>User</strong><br />

BIC r1, r0, #0x1f<br />

ORR r1, r1, #0x12<br />

MSR CPSR_c, r1<br />

;Keep 32 bytes for Abort mode stack<br />

SUB sp,r2,#0x7F<br />

; Return to the original mode.<br />

MSR CPSR_c, r0<br />

; Initialize the stack for user application<br />

; Keep 256 bytes for IRQ mode stack<br />

SUB sp,r2,#0x17F<br />

; /*********************************************************************<br />

; * Setup Vectored Interrupt controller. DCC Rx and Tx interrupts<br />

; * generate Non Vectored IRQ request. rm_init_entry is aware<br />

; * of the VIC and it enables the DBGCommRX and DBGCommTx interrupts.<br />

; * Default vector address register is programmed with the address of<br />

; * Non vectored app_irqDispatch mentioned in this example. <strong>User</strong> can setup<br />

; * Vectored IRQs or FIQs here.<br />

; *********************************************************************/<br />

VICBaseAddr EQU 0xFFFFF000 ; VIC Base address<br />

VICDefVectAddrOffset EQU 0x34<br />

LDR r0, =VICBaseAddr<br />

LDR r1, =app_irqDispatch<br />

STR r1, [r0,#VICDefVectAddrOffset]<br />

BL rm_init_entry ;Initialize RealMonitor<br />

;enable FIQ and IRQ in ARM Processor<br />

MRS r1, CPSR ; get the CPSR<br />

BIC r1, r1, #0xC0 ; enable IRQs and FIQs<br />

MSR CPSR_c, r1 ; update the CPSR<br />

; /*********************************************************************<br />

; * Get the address of the <strong>User</strong> entry point.<br />

; *********************************************************************/<br />

LDR lr, =<strong>User</strong>_Entry<br />

MOV pc, lr<br />

; /*********************************************************************<br />

; * Non vectored irq handler (app_irqDispatch)<br />

; *********************************************************************/<br />

AREA app_irqDispatch, CODE<br />

VICVectAddrOffset EQU 0x30<br />

app_irqDispatch<br />

;enable interrupt nesting<br />

STMFD sp!, {r12,r14}<br />

MRS r12, spsr ;Save SPSR in to r12<br />

MSR cpsr_c,0x1F ;Re-enable IRQ, go to system mode<br />

;<strong>User</strong> should insert code here if non vectored Interrupt sharing is<br />

;required. Each non vectored shared irq handler must return to<br />

;the interrupted instruction by using the following code.<br />

;MSR cpsr_c, #0x52 ;Disable irq, move to IRQ mode<br />

<strong>LPC2131</strong>/<strong>2132</strong>/<strong>2138</strong><br />

RealMonitor 261 November 22, 2004