You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Philips Semiconductors Preliminary <strong>User</strong> <strong>Manual</strong><br />

ARM-based Microcontroller<br />

<strong>LPC2131</strong>/<strong>2132</strong>/<strong>2138</strong><br />

asserting the ARM7TDMI-S local bus signal CLKEN.) Under some conditions, this delay could result in a Watchdog time-out. The<br />

user will need to be aware of this possibility and take steps to insure that an unwanted Watchdog reset does not cause a system<br />

failure while programming or erasing the Flash memory.<br />

In order to preclude the possibility of stale data being read from the Flash memory, the <strong>LPC2131</strong>/<strong>2132</strong>/<strong>2138</strong> MAM holding latches<br />

are automatically invalidated at the beginning of any Flash programming or erase operation. Any subsequent read from a Flash<br />

address will cause a new fetch to be initiated after the Flash operation has completed.<br />

MEMORY ACCELERATOR MODULE OPERATING MODES<br />

Three modes of operation are defined for the MAM, trading off performance for ease of predictability:<br />

0) MAM off. All memory requests result in a Flash read operation (see note 2 below). There are no instruction prefetches.<br />

1) MAM partially enabled. Sequential instruction accesses are fulfilled from the holding latches if the data is present. Instruction<br />

prefetch is enabled. Non-sequential instruction accesses initiate Flash read operations (see note 2 below). This means that all<br />

branches cause memory fetches. All data operations cause a Flash read because buffered data access timing is hard to predict<br />

and is very situation dependent.<br />

2) MAM fully enabled. Any memory request (code or data) for a value that is contained in one of the corresponding holding latches<br />

is fulfilled from the latch. Instruction prefetch is enabled. Flash read operations are initiated for instruction prefetch and code or<br />

data values not available in the corresponding holding latches.<br />

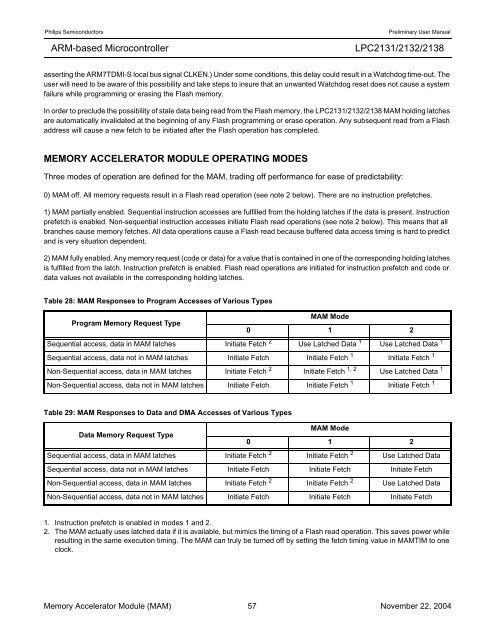

Table 28: MAM Responses to Program Accesses of Various Types<br />

MAM Mode<br />

Program Memory Request Type<br />

0 1 2<br />

Sequential access, data in MAM latches Initiate Fetch 2<br />

Use Latched Data 1<br />

Use Latched Data 1<br />

Sequential access, data not in MAM latches Initiate Fetch Initiate Fetch 1<br />

Initiate Fetch 1<br />

Non-Sequential access, data in MAM latches Initiate Fetch 2 Initiate Fetch 1, 2 Use Latched Data 1<br />

Non-Sequential access, data not in MAM latches Initiate Fetch Initiate Fetch 1<br />

Table 29: MAM Responses to Data and DMA Accesses of Various Types<br />

Data Memory Request Type<br />

MAM Mode<br />

Initiate Fetch 1<br />

0 1 2<br />

Sequential access, data in MAM latches Initiate Fetch 2 Initiate Fetch 2 Use Latched Data<br />

Sequential access, data not in MAM latches Initiate Fetch Initiate Fetch Initiate Fetch<br />

Non-Sequential access, data in MAM latches Initiate Fetch 2 Initiate Fetch 2 Use Latched Data<br />

Non-Sequential access, data not in MAM latches Initiate Fetch Initiate Fetch Initiate Fetch<br />

1. Instruction prefetch is enabled in modes 1 and 2.<br />

2. The MAM actually uses latched data if it is available, but mimics the timing of a Flash read operation. This saves power while<br />

resulting in the same execution timing. The MAM can truly be turned off by setting the fetch timing value in MAMTIM to one<br />

clock.<br />

Memory Accelerator Module (MAM) 57 November 22, 2004