You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Philips Semiconductors Preliminary <strong>User</strong> <strong>Manual</strong><br />

ARM-based Microcontroller<br />

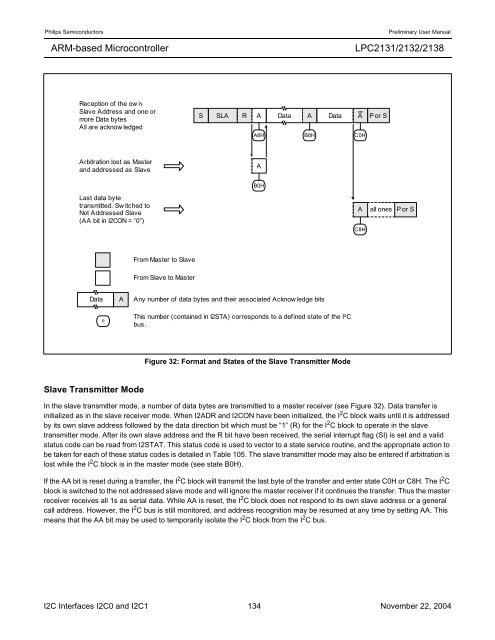

Reception of the ow n<br />

Slave Address and one or<br />

more Data bytes<br />

All are acknow ledged<br />

Arbitration lost as Master<br />

and addressed as Slave<br />

Last data byte<br />

transmitted. Sw itched to<br />

Not Addressed Slave<br />

(AA bit in I2CON = “0”)<br />

Data A<br />

Slave Transmitter Mode<br />

n<br />

From Master to Slave<br />

From Slave to Master<br />

S SLA R A Data A Data A<br />

P or S<br />

A8H B8H C0H<br />

This number (contained in I2STA) corresponds to a defined state of the I 2 C<br />

bus.<br />

Figure 32: Format and States of the Slave Transmitter Mode<br />

<strong>LPC2131</strong>/<strong>2132</strong>/<strong>2138</strong><br />

all ones<br />

In the slave transmitter mode, a number of data bytes are transmitted to a master receiver (see Figure 32). Data transfer is<br />

initialized as in the slave receiver mode. When I2ADR and I2CON have been initialized, the I 2 C block waits until it is addressed<br />

by its own slave address followed by the data direction bit which must be “1” (R) for the I 2 C block to operate in the slave<br />

transmitter mode. After its own slave address and the R bit have been received, the serial interrupt flag (SI) is set and a valid<br />

status code can be read from I2STAT. This status code is used to vector to a state service routine, and the appropriate action to<br />

be taken for each of these status codes is detailed in Table 105. The slave transmitter mode may also be entered if arbitration is<br />

lost while the I 2 C block is in the master mode (see state B0H).<br />

If the AA bit is reset during a transfer, the I 2 C block will transmit the last byte of the transfer and enter state C0H or C8H. The I 2 C<br />

block is switched to the not addressed slave mode and will ignore the master receiver if it continues the transfer. Thus the master<br />

receiver receives all 1s as serial data. While AA is reset, the I 2 C block does not respond to its own slave address or a general<br />

call address. However, the I 2 C bus is still monitored, and address recognition may be resumed at any time by setting AA. This<br />

means that the AA bit may be used to temporarily isolate the I 2 C block from the I 2 C bus.<br />

I2C Interfaces I2C0 and I2C1 134 November 22, 2004<br />

A<br />

B0H<br />

Any number of data bytes and their associated Acknow ledge bits<br />

A<br />

C8H<br />

P or S