Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Philips Semiconductors Preliminary <strong>User</strong> <strong>Manual</strong><br />

ARM-based Microcontroller<br />

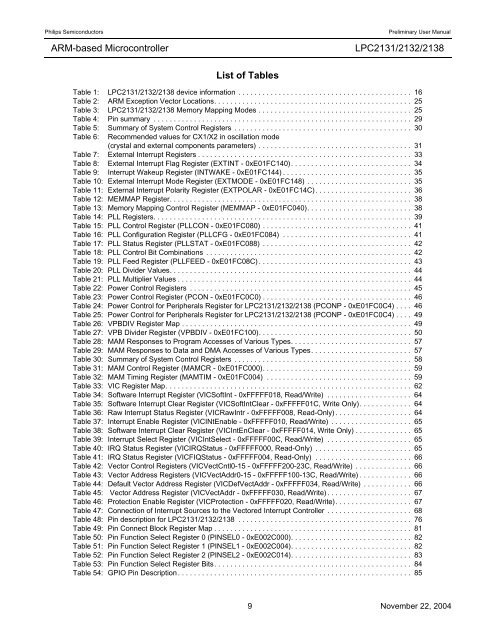

List of Tables<br />

<strong>LPC2131</strong>/<strong>2132</strong>/<strong>2138</strong><br />

Table 1: <strong>LPC2131</strong>/<strong>2132</strong>/<strong>2138</strong> device information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16<br />

Table 2: ARM Exception Vector Locations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25<br />

Table 3: <strong>LPC2131</strong>/<strong>2132</strong>/<strong>2138</strong> Memory Mapping Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25<br />

Table 4: Pin summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29<br />

Table 5: Summary of System Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30<br />

Table 6: Recommended values for CX1/X2 in oscillation mode<br />

(crystal and external components parameters) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31<br />

Table 7: External Interrupt Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33<br />

Table 8: External Interrupt Flag Register (EXTINT - 0xE01FC140). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34<br />

Table 9: Interrupt Wakeup Register (INTWAKE - 0xE01FC144) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35<br />

Table 10: External Interrupt Mode Register (EXTMODE - 0xE01FC148) . . . . . . . . . . . . . . . . . . . . . . . . . . 35<br />

Table 11: External Interrupt Polarity Register (EXTPOLAR - 0xE01FC14C). . . . . . . . . . . . . . . . . . . . . . . . 36<br />

Table 12: MEMMAP Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38<br />

Table 13: Memory Mapping Control Register (MEMMAP - 0xE01FC040). . . . . . . . . . . . . . . . . . . . . . . . . . 38<br />

Table 14: PLL Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39<br />

Table 15: PLL Control Register (PLLCON - 0xE01FC080) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41<br />

Table 16: PLL Configuration Register (PLLCFG - 0xE01FC084) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41<br />

Table 17: PLL Status Register (PLLSTAT - 0xE01FC088) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42<br />

Table 18: PLL Control Bit Combinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42<br />

Table 19: PLL Feed Register (PLLFEED - 0xE01FC08C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43<br />

Table 20: PLL Divider Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44<br />

Table 21: PLL Multiplier Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44<br />

Table 22: Power Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45<br />

Table 23: Power Control Register (PCON - 0xE01FC0C0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46<br />

Table 24: Power Control for Peripherals Register for <strong>LPC2131</strong>/<strong>2132</strong>/<strong>2138</strong> (PCONP - 0xE01FC0C4) . . . . 46<br />

Table 25: Power Control for Peripherals Register for <strong>LPC2131</strong>/<strong>2132</strong>/<strong>2138</strong> (PCONP - 0xE01FC0C4) . . . . 49<br />

Table 26: VPBDIV Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49<br />

Table 27: VPB Divider Register (VPBDIV - 0xE01FC100). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50<br />

Table 28: MAM Responses to Program Accesses of Various Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57<br />

Table 29: MAM Responses to Data and DMA Accesses of Various Types. . . . . . . . . . . . . . . . . . . . . . . . . 57<br />

Table 30: Summary of System Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58<br />

Table 31: MAM Control Register (MAMCR - 0xE01FC000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59<br />

Table 32: MAM Timing Register (MAMTIM - 0xE01FC004) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59<br />

Table 33: VIC Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62<br />

Table 34: Software Interrupt Register (VICSoftInt - 0xFFFFF018, Read/Write) . . . . . . . . . . . . . . . . . . . . . 64<br />

Table 35: Software Interrupt Clear Register (VICSoftIntClear - 0xFFFFF01C, Write Only). . . . . . . . . . . . . 64<br />

Table 36: Raw Interrupt Status Register (VICRawIntr - 0xFFFFF008, Read-Only) . . . . . . . . . . . . . . . . . . . 64<br />

Table 37: Interrupt Enable Register (VICINtEnable - 0xFFFFF010, Read/Write) . . . . . . . . . . . . . . . . . . . . 65<br />

Table 38: Software Interrupt Clear Register (VICIntEnClear - 0xFFFFF014, Write Only) . . . . . . . . . . . . . . 65<br />

Table 39: Interrupt Select Register (VICIntSelect - 0xFFFFF00C, Read/Write) . . . . . . . . . . . . . . . . . . . . . 65<br />

Table 40: IRQ Status Register (VICIRQStatus - 0xFFFFF000, Read-Only) . . . . . . . . . . . . . . . . . . . . . . . . 65<br />

Table 41: IRQ Status Register (VICFIQStatus - 0xFFFFF004, Read-Only) . . . . . . . . . . . . . . . . . . . . . . . . 66<br />

Table 42: Vector Control Registers (VICVectCntl0-15 - 0xFFFFF200-23C, Read/Write) . . . . . . . . . . . . . . 66<br />

Table 43: Vector Address Registers (VICVectAddr0-15 - 0xFFFFF100-13C, Read/Write) . . . . . . . . . . . . . 66<br />

Table 44: Default Vector Address Register (VICDefVectAddr - 0xFFFFF034, Read/Write) . . . . . . . . . . . . 66<br />

Table 45: Vector Address Register (VICVectAddr - 0xFFFFF030, Read/Write) . . . . . . . . . . . . . . . . . . . . . 67<br />

Table 46: Protection Enable Register (VICProtection - 0xFFFFF020, Read/Write). . . . . . . . . . . . . . . . . . . 67<br />

Table 47: Connection of Interrupt Sources to the Vectored Interrupt Controller . . . . . . . . . . . . . . . . . . . . . 68<br />

Table 48: Pin description for <strong>LPC2131</strong>/<strong>2132</strong>/<strong>2138</strong> . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76<br />

Table 49: Pin Connect Block Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81<br />

Table 50: Pin Function Select Register 0 (PINSEL0 - 0xE002C000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82<br />

Table 51: Pin Function Select Register 1 (PINSEL1 - 0xE002C004). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82<br />

Table 52: Pin Function Select Register 2 (PINSEL2 - 0xE002C014). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83<br />

Table 53: Pin Function Select Register Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84<br />

Table 54: GPIO Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85<br />

9 November 22, 2004