Note; If the word count ~ 28, the effective doubleword(ED) is pulled from memory stack locations (relativeaddresses initial TSA-24 and initial TSA+l).If the word count=O, the ED is pulled from realmemory locations 2 and 3.Status Stack Pointer Doubleword; (Only if initial WordCount ~ 28)TSA-1 --TSA until terminal TSA = initial TSA-28;Word Count - 1 --Word Count unti I terminal WordCount = initial Word Count - 28 (if initial Word Count> 32,767, bit 48 not affected); and,Space Count + 1 - Space Count untir terminal SpaceCount = initial Space Count + 28 (if Space Count> 32,767, then set bit 32 to 1).Interrupt System;. If (1)10 = 1 and (1)11 = 1, clear and arm interruptlevel.If (1)10 = 1 and (1)11 = 0, clear and disarm interruptlevel.EXECUTE/BRANCHINSTRUCT~NS<strong>The</strong> following instructions can cause the basic processor toexecute instructions in an order other than that of sequentiallyascending instruction addresses:NONALLOWED OPERATION TRAP DURING EXECUTIONOF BRANCH -INSTRUCTION<strong>The</strong> next instruction after a branch instruction may residein two possible places: the location following the branchinstruction or a location designated by the branch instruction.Either of these two locations may be in a protectedmemory region or in a region that is physically nonexist~nt.<strong>The</strong> executio-n of th~ branch does not cause a trap un lessthe instruction that is actually to follow the branch instructionis in a protected or nonexistent memory region. Trapsdo not occur because of any anticipation on the part of thehardware.A nonallowed operation trap condition during execution ofa branch instruction wi II occur for the following reasons;<strong>1.</strong> <strong>The</strong> branch instruction -is indirectly addressed~ and thebranch conditions are satisfied, but the address of thelocation containing the direct address is either nonexistentor unavai lable for read access fo the programin the slave mode.2. <strong>The</strong> branch instruction is unconditional (or the branchis conditional and the condition for the branch is satisfied),but the effective address of the branch instructionis either nonexistent or unavailable for instructionor read access to the program (in slave -or masterprotectedmode).If either of the above situations occurs, the basic processoraborts execution of the branch instruction and executes anonallowed operation trap.Instruction NameExecuteBranch on Conditions SetBranch on Conditions ResetBranch on Incrementing RegisterBranch on Decrementing RegisterBranch and LinkMnemonicEXUBCSBCRBIRBDRBALPrior to the time that an instruction is accessed from memoryfor execution, bit positions 15-31 of the program statuswords contain the virtual address of the instruction~ referredto as the instruction address. At this time, the basic processortraps to location X'40' if the actual address of theinstruction is nonexistent or instruction-access protected.If the instruction address is existent and is not instructionaccessprotected, the instruction is accessed and the instructionaddress portion of the program status words isincremented by 1, so that it now contains the virtual addressof the next instruction in sequence {referred to as th~ updatedinstruction address}.<strong>The</strong> EXECUTE instruction can be used to insert another instructioninto the program sequence, and the branch instructionscan be used to alter the program sequence, eitherunconditionally or conditionally. If a branch is unconditiona!(or conditional and the branch condHion is satisfied),the instruction pointed to by the effective address of thebranch instruction is normally the next instruction to beexecuted. If a branch is conditional and the conditionfor the branch is not satisfied, the next instruction is normallytaken from the next location, in ascending sequence,after the branch instruction.If a trap condition occurs during the execulion sequence ofany instruction, the basic proces~r decrements the updatedinstruction address by 1 and then traps to the location assignedto the trap condition. If neither a trap conditionnor a satisfied branch condition occurs during the executionof an instruction, the next instruction is accessed from thelocation pointed to by the updated instruction address. Ifa satisfied branch condition occurs during the execution ofa branch instruction (and no trap condition occurs), thenext instruction is accessed from the location pointed to bythe effective address of the branch instruction.106 Execute/Branch Instructions

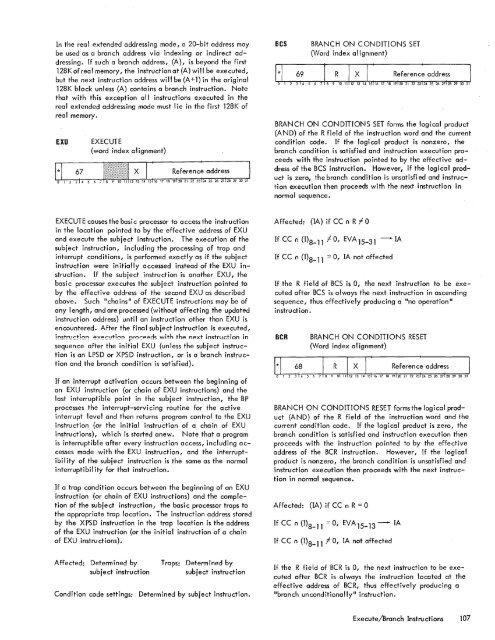

In the real extended addressing mode, a 20-bit address maybe used as a branch address via indexing or indirect addressing.If such a branch address, (A), is beyond the first128Kofreal memory, the instruction at (A) will be executed,but the next instruction address will be (A+1) in the original128K block unless (A) contains a branch instruction. Notethat with this exception all instructions executed in thereal extended addressing mode must lie in the first 128K ofrea I memory.EXUEXECUTE(word index alignment)BCSBRANCH ON CONDITIONS SET(Word index alignment)BRANCH ON CONDITIONS SET forms the logical product(AND) of the R field of the instruction word and the currentcondition code. If the logical product is nonzero, thebranch condition is satisfied and instruction execution proceedswith the instruction pointed to by the effective addressof the BCS instruction. However, if the logical productis zero, the branch condition is unsatisfi ed and instructionexecution then proceeds with the next instruction innormal sequence.EXECUTE causes the basic processor to access the instructionin the location pointed to by the effective address of EXUand execute the subject instruction. <strong>The</strong> execution of thesubject instruction, including the processing of trap andinterrupt conditions, is performed exactly as if the subjectinstruction were initially accessed instead of the EXU instruction.If the subject instruction is another EXU, thebasic processor executes the subject instruction pointed toby the effective address of the second EXU as describedabove. Such "chains" of EXECUTE instructions may be ofany length, and are processed (without affecting the updatedinstruction address) until an instruction other than EXU isencountered. After the final subject instruction is executed,inc:for"rtit"ln ..._.. __.. _-- Pypr"tit"ln ----------- nrt"lrpp,.lc;. r------_· with thp. np.xt instruction insequence after the initial EXU (unless the subject instructionis an LPSD or XPSD instruction, or is a branch instructionand the branch condition is satisfied).If an interrupt activation occurs between the beginning ofan EXU instruction (or chain of EXU instructions) and thelast interruptible point in the subject instruction, the BPprocesses the interrupt-servicing routine for the activeinterrupt level and then returns program control to the EXUinstruction (or the initial instruction of a chain of EXUinstructions), which is started anew. Note that a programis interruptible after every instruction access, including accessesmade with the EXU instruction, and the interruptibilityof the subject instruction is the same as the normalinterruptibility for that instruction.If a trap condition occurs between the beginning of an EXUinstruction (or chain of EXU instructions) and the completionof the subject instruction, the basic processor traps tothe appropriate trap location. <strong>The</strong> instruction address storedby the XPSD instruction in the trap location is the addressof the EXU instruction (or the initial instruction of a chainof EXU instructions).Affected: (lA) if CC n R f 0If CC n (1)8_11/0, EVA 15 - 31 -IAIf CC n (1)8-11 = 0, IA not affectedIf the R field of BCS is 0, the next instruction to be executedafter BCS is always the next instruction in ascendingsequence, thus effectively producing a "no operation IIinstruction.BCRBRANCH ON CONDITIONS RESET(Word index alignment)BRANCH ON CONDITIONS RESET forms the logical product(AND) of the R field of the instruction word and thecurrent condition code. If the logical product is zero, thebranch condition is satisfied and instruction execution thenproceeds with the instruction pointed to by the effectiveaddress of the BCR instruction. However, if the logicalproduct is nonzero, the branch condition is unsatisfied andinstruction execution then proceeds with the next instructionin normal sequence.Affected: (IA) if CC n R = 0If CC n (1)8-11 = 0, EVA 15_ 13-If CC n (1)8-11 10, IA not affectedIAAffected: Determined bysubject instructionT raps: Determined bysubject instructionCondition code settings: Determined by subject instruction.If the R field of BCR is 0, the next instruction to be executedafter BCR is always the instruction located at theeffective address of BCR, thus effectively producing a"branch unconditionally" instruction.Execute/Branch Instructions 107

- Page 1 and 2:

Xerox 560 ComputerReference Manual9

- Page 5 and 6:

4. INPUT/OUTPUT OPERA TIO NS 142 AG

- Page 7 and 8:

1. XEROX 560 COMPUTER SYSTEMINTRODU

- Page 10 and 11:

Many operations are performed in fl

- Page 12 and 13:

Rapid Context Switching. When respo

- Page 14 and 15:

2. SYSTEM ORGANIZATIONThe elements

- Page 16:

FAST MEMORYARITHMETIC AND CONTROL U

- Page 19 and 20:

INFORMATION BOUNDARIESBasic process

- Page 21 and 22:

(Maximumof eight)Core Core Core Cor

- Page 23 and 24:

3. Diagnostic logic. Each memory dr

- Page 25 and 26:

eference address field of the instr

- Page 27 and 28:

Instruction in memory:Instruction i

- Page 29 and 30:

Real-extended addressing is specifi

- Page 31:

Table 1. Basic Processor Operating

- Page 35 and 36:

DesignationFunctionDesignationFunct

- Page 37 and 38:

InterruptStateDisarmedArmed[$Waitin

- Page 39 and 40:

AddressTable 2. Interrupt Locations

- Page 41 and 42:

is assumed to contain an XPSD or a

- Page 43 and 44:

Table 3. Summary of Trap LocationsL

- Page 45 and 46:

TRAP MASKSThe programmer may mask t

- Page 47 and 48:

PUSH-DOWN STACK LIMIT TRAPPush-down

- Page 49 and 50:

Instruction Name Mnemonic FaultDeci

- Page 51 and 52:

subroutine. However, with certain c

- Page 53 and 54:

3. INSTRUCTION REPERTOIREThis chapt

- Page 55 and 56:

CC1 is unchanged by the instruction

- Page 57 and 58:

Condition code settings:2 3 4 Resul

- Page 59 and 60:

Example 2, odd R field value:Before

- Page 61 and 62: significance (FS), floating zero (F

- Page 63 and 64: next sequential register after regi

- Page 65 and 66: R 1 R2 R3 MeaningoThe effective vir

- Page 67 and 68: Condition code settings:2 3 4 Resul

- Page 69 and 70: MIMULTIPLY IMMEDIATE(Immediate oper

- Page 71 and 72: original contents of register R, re

- Page 73 and 74: Instruction NameCompare HalfwordMne

- Page 75 and 76: Condition code settings:2 3 4 Resul

- Page 77 and 78: 2 3 4 Result of ShiftCircular Shift

- Page 79 and 80: 4. At the completion of the left sh

- Page 81 and 82: Instruction NameFloating Subtract L

- Page 83 and 84: The following table shows the possi

- Page 85 and 86: Table 8.Condition Code Settings for

- Page 87 and 88: PACKED DECIMAL NUMBERSAll decimal a

- Page 89 and 90: DSTDECIMAL STORE(Byte index alignme

- Page 91 and 92: If no indirect addressing or indexi

- Page 93 and 94: Instruction NameMnemonicDesignation

- Page 95 and 96: Both byte strings are C bytes in le

- Page 97 and 98: of the destination byte that caused

- Page 99 and 100: again present, unti I a positive or

- Page 101 and 102: The new contents of register 7 are:

- Page 103 and 104: traps to location X'42 1 as a resul

- Page 105 and 106: If there is sufficient space in the

- Page 107 and 108: If CC1, or CC3, or both CC1 and CC3

- Page 109 and 110: appropriate memory stack locations

- Page 111: II, EI) are generated by II ORing"

- Page 115 and 116: CAll INSTRUCTIONSEach ofthe four CA

- Page 117 and 118: The XPSD instruction' is used for t

- Page 119 and 120: If (I)1O = 0, trap or interrupt ins

- Page 121 and 122: For either memory map format and ei

- Page 123 and 124: initial value plus the initial valu

- Page 125 and 126: Table 9. Status Word 0Field Bits Co

- Page 127 and 128: READ INTERRUPT INHIBITSThe followin

- Page 129 and 130: Table 11.Read Direct Mode 9 Status

- Page 131 and 132: SET ALARM INDICATORThe following co

- Page 133 and 134: INPUT jOUTPUT INSTRUCTIONSThe I/o i

- Page 135 and 136: Table 13.Description of I/o Instruc

- Page 137 and 138: Table 15.Device Status Byte (Regist

- Page 139 and 140: Table 16. Operational Status Byte (

- Page 141 and 142: Table 19.Status Response Bits for A

- Page 143 and 144: If CC4 = 0, the MIOP is in a normal

- Page 145 and 146: 2 3 4 Meaningo 0 I/o address not re

- Page 147 and 148: The functions of bits within the DC

- Page 149 and 150: 4. Each unit-record controller (int

- Page 151 and 152: Interrupt at Channel End (Bit Posit

- Page 153 and 154: Transfer in Channel. A control lOCO

- Page 155 and 156: Otherwise, the first word of the ne

- Page 157 and 158: Depending upon the characteristics

- Page 159 and 160: change the rate on the primary cons

- Page 161 and 162: Location(hex) (dec)20 3221 3322 342

- Page 163 and 164:

Table 22.Diagnostic Control (P-Mode

- Page 165 and 166:

at its normal rate (e. g., fixed du

- Page 167 and 168:

SET LOW CLOCK MARGINSThis command c

- Page 169 and 170:

BP STATUS AND NO.Th i s group of i

- Page 171 and 172:

Input5MPri ntout5MFunctionStore X 1

- Page 173 and 174:

6. SYSTEM CONFIGURATION CONTROLPool

- Page 175 and 176:

Table 25. Functions of Processor Cl

- Page 177:

Table 26. Functions of Memory Unit

- Page 180 and 181:

STANDARD 8-BIT COMPUTER CODES (EBCD

- Page 182 and 183:

STANDARD SYMBOL-CODE CORRESPONDENCE

- Page 184 and 185:

STANDARD SYMBOL-CODE CORRESPONDENCE

- Page 186 and 187:

TABLE OF POWERS OF SIXTEEN II162564

- Page 188 and 189:

HEXADECIMAL-DECIMAL INTEGER CONVERS

- Page 190 and 191:

HEXADECIMAL-DECIMAL INTEGER CONVERS

- Page 192 and 193:

HEXADECIMAL-DECIMAL INTEGER CONVERS

- Page 194 and 195:

HEXADECIMAL-DECIMAL FRACTION CONVER

- Page 196 and 197:

HEXADECIMAL-DECIMAL FRACTION CONVER

- Page 198 and 199:

APPENDIX B.GLOSSARY OF SYMBOLIC TER

- Page 200 and 201:

TermMeaningTermMeaningWKxWrite key

- Page 202 and 203:

Table C-2. Memory Unit Status Regis

- Page 204 and 205:

Y OYf'lV r'f'lrnf'lrtil"\n'''' ....

- Page 206:

701 South Aviation BoulevardEI Segu