1. xerox 560 computer system - The UK Mirror Service

1. xerox 560 computer system - The UK Mirror Service

1. xerox 560 computer system - The UK Mirror Service

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

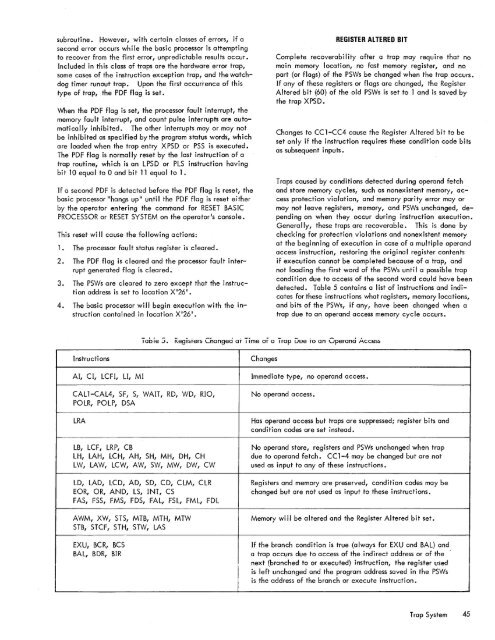

subroutine. However, with certain classes of errors, if asecond error occurs while the basic processor is attemptingto recover from the first error, unpredictable results occur.Inc I uded in th is c lass of traps are the hardware error trap,some cases of the instruction exception trap, and the watchdogtimer runout trap. Upon the first occurrence of thistype of trap, the PDF flag is set.When the PDF flag is set, the processor fault interrupt, thememory fault interrupt, and count pulse interrupts are automaticallyinhibited. <strong>The</strong> other interrupts mayor may notbe inhibited as specified by the program status words, whichare loaded when the trap entry XPSD or PSS is executed.<strong>The</strong> PDF flag is normally reset by the last instruction of atrap routine, which is an LPSD or PLS instruction havingbit 10 equal to 0 and bit 11 equal to <strong>1.</strong>If a second PDF is detected before the PDF flag is reset, thebasic processor "hangs Up" unti I the PDF flag is reset eitherby the operator entering the command for RESET BASICPROCESSOR or RESET SYSTEM on the operator1s console.This reset wi II cause the following actions:<strong>1.</strong> <strong>The</strong> processor fault status register is cleared.2. <strong>The</strong> PDF flag is cleared and the processor fault interruptgenerated flag is cleared.3. <strong>The</strong> PSWs are cleared to zero except that the instructionaddress is set to location X 126 1 •4. <strong>The</strong> basic processor will begin execution with the instructioncontained in location X126 1 .REGISTER ALTERED BITComplete recoverability after a trap may require that nomain memory location, no fast memory register, and nopart (or flags) of the PSWs be changed when the trap occurs.If any of these registers or flags are changed, the RegisterAltered bit (60) of the old PSWs is set to 1 and is saved bythe trap XPSD.Changes to CC1-CC4 cause the Register Altered bit to beset only if the instruction requires these condition code bitsas subsequent inputs.Traps caused by conditions detected during operand fetchand store memory cycles, such as nonexistent memory, accessprotection violation, and memory parity error mayormay not leave registers, memory, and PSWs unchanged, dependingon when they occur during instruction execution.Generally, these traps are recoverable. This is done bychecking for protection violations and nonexistent memoryat the beginning of execution in case of a multiple operandaccess instruction, restoring the original register contentsif execution cannot be completed because of a trap, andnot loading the first word of the PSWs until a possible trapcondition due to access of the second word could have beendetected. Table 5 contains a list of instructions and indicatesfor these instructions what registers, memory locations,and bits of the PSWs, if any, have been changed when atrap due to an operand access memory cycle occurs.Tabie 5. RegiSTers Changed aT Time or a Trap Due TO an Operand AccessInstructi onsAI, CI, LCFI, LI, MICALl-CAL4, SF,S, WAIT, RD, WD, RIO,POLR, POLP, DSALRALB, LCF, LRP, CBLH, LAH, LCH, AH, SH, MH, DH, CHLW, LAW, LCW, AW, SW, MW, OW, CWLD, LAD, LCD, AD, SO, CD, CLM, CLREaR, OR, AND, LS, INT, CSFAS, FSS, FMS, FDS, FAL, FSL, FML, FDLAWM, XW, STS, MTB, MTH, MTWSTB, STCF, 5TH, STW, LASEXU, BCR, BCSBAL, BDR, BIRChangesImmediate type, no operand access.No operand access.Has operand access but traps are suppressed; register bits andcondition codes are set instead.No operand store, registers and PSWs unchanged when trapdue to operand fetch. CCl-4 may be changed but are notused as input to any of these instructions.Registers and memory are preserved, condition codes may bechanged but are not used as input to these instructions.Memory will be altered and the Register Altered bit set.If the branch condition is true (always for EXU and BAL) anda trap occurs due to access of the indirect address or of thenext (branched to or executed) instruction, the register usedis left unchanged and the program address saved in the PSWsis the address of the branch or execute instruction.Trap System 45