1. xerox 560 computer system - The UK Mirror Service

1. xerox 560 computer system - The UK Mirror Service

1. xerox 560 computer system - The UK Mirror Service

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

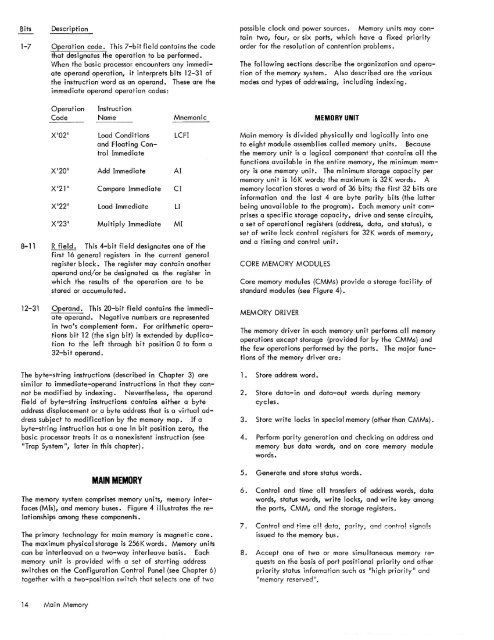

Bits1-7DescriptionOperation code. This 7-bit field contains the codethat designates the operation to be performed.When the basic processor encounters any immediateoperand operation, it interprets bits 12-31 ofthe instruction word as an operand. <strong>The</strong>se are theimmediate operand operation codes:possible clock and power sources. Memory units may containtwo, four, or six ports, which have a fixed priorityorder for the resolution of contention problems.<strong>The</strong> following sections describe the organization and operationof the memory <strong>system</strong>. Also described are the variousmodes and types of addressing, including indexing.OperationCodeInstructionNameMnemonicMEMORY UNIT8-1112-31X'02 1X '21 1X '22 1X'23 1Load Conditionsand Floating ControlImmediateAdd ImmediateCompare ImmediateLoad ImmediateMultiply ImmediateLCFIR field. This 4-bit field designates one of thefirst 16 general registers in the current generalregister block. <strong>The</strong> register may contain anotheroperand and/or be designated as the register inwhich the results of the operation are to bestored or a ccumu la ted.Operand. This 20-bit field contains the immediateoperand. Negative numbers are representedin two1s complement form. For arithmetic operationsbit 12 (the sign bit) is extended by duplicationto the left through bit position 0 to form a32-bit operand.AICILIMIMain memory is divided physically and logically into oneto eight module assemblies called memory units. Becausethe memory unit is a logical component that contains all thefunctions available in the entire memory, the minimum memoryis one memory unit. <strong>The</strong> minimum storage capacity permemory unit is 16K words; the maximum is 32K words. Amemory location stores a word of 36 bits; the first 32 bits areinformation and the last 4 are byte parity bits (the latterbeing unavai lable to the program). Each memory unit comprisesa specific storage capacity, drive and sense circuits,a set of operational registers (address, data, and status), aset of write lock control registers for 32K words of memory,and a timing and control unit.CORE MEMORY MODULESCore memory modules (CMMs) provide a storage facility ofstandard modules (see Figure 4).MEMORY DRIVER<strong>The</strong> memory driver in each memory unit performs all memoryoperations except storage (provided for by the CMMs) andthe few operations performed by the ports. <strong>The</strong> major functionsof the memory driver are:<strong>The</strong> byte-string instructions (described in Chapter 3) aresimi lar to immediate-operand instructions in that they cannotbe modified by indexing. Nevertheless, the operandfield of byte-string instructions contains either a byteaddress displacement or a byte address that is a virtual addresssubject to modification by the memory map. If abyte-string instruction has a one in bit position zero, thebasic processor treats it as a nonexistent instruction (see"Trap System ", later in this chapter).MAIN MEMORY<strong>The</strong> memory <strong>system</strong> comprises memory units, memory interfaces(MIs), and memory buses. Figure 4 illustrates the relationshipsamong these components.<strong>The</strong> primary technology for main memory is magnetic core.<strong>The</strong> maximum physical storage is 256Kwords. Memory unitscan be interleaved on a two-way interleave basis. Eachmemory unit is provided with a set of starting addressswitches on the Configuration Control Panel (see Chapter 6)together with a two-position switch that selects one of two1 • Store address word.2. Store data-in and data-out words during memorycycles.3. Store write locks in special memory (other than CMMs).4. Perform parity generation and checking on address andmemory bus data words, and on core memory modulewords.5. Generate and store status words.6. Control and time all transfers of address words, datawords, status words, write locks, and write key amongthe ports, CMM, and the storage registers.7. Control and time a!! data, parity, and. control signalsissued to the memory bus.8. Accept one of two or more simultaneous memory requestson the basis of port positional priority and otherpriority status information such as "high priority" and"memory reserved ".14 Main Memory