PCT/1998/43 - World Intellectual Property Organization

PCT/1998/43 - World Intellectual Property Organization

PCT/1998/43 - World Intellectual Property Organization

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

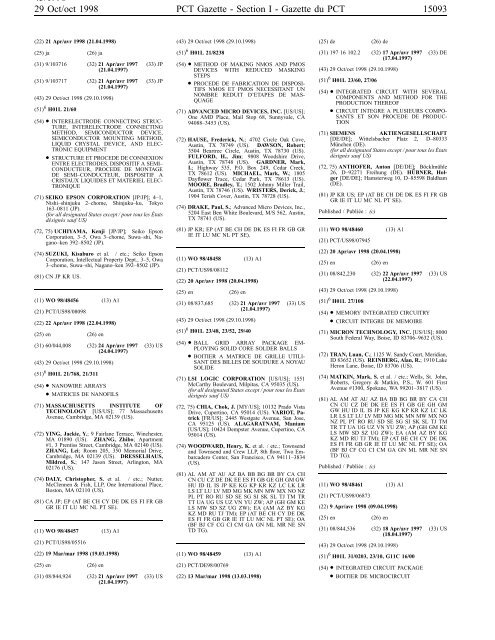

<strong>43</strong>/<strong>1998</strong><br />

29 Oct/oct <strong>1998</strong> <strong>PCT</strong> Gazette - Section I - Gazette du <strong>PCT</strong> 15093<br />

(22) 21 Apr/avr <strong>1998</strong> (21.04.<strong>1998</strong>)<br />

(25) ja (26) ja<br />

(31) 9/103716 (32) 21 Apr/avr 1997<br />

(21.04.1997)<br />

(31) 9/103717 (32) 21 Apr/avr 1997<br />

(21.04.1997)<br />

(33) JP<br />

(33) JP<br />

(<strong>43</strong>) 29 Oct/oct <strong>1998</strong> (29.10.<strong>1998</strong>)<br />

(51) 6 H01L 21/60<br />

(54) • INTERELECTRODE CONNECTING STRUC-<br />

TURE, INTERELECTRODE CONNECTING<br />

METHOD, SEMICONDUCTOR DEVICE,<br />

SEMICONDUCTOR MOUNTING METHOD,<br />

LIQUID CRYSTAL DEVICE, AND ELEC-<br />

TRONIC EQUIPMENT<br />

•<br />

STRUCTURE ET PROCEDE DE CONNEXION<br />

ENTRE ELECTRODES, DISPOSITIF A SEMI–<br />

CONDUCTEUR, PROCEDE DE MONTAGE<br />

DE SEMI–CONDUCTEUR, DISPOSITIF A<br />

CRISTAUX LIQUIDES ET MATERIEL ELEC-<br />

TRONIQUE<br />

(71) SEIKO EPSON CORPORATION [JP/JP]; 4–1,<br />

Nishi–shinjuku 2–chome, Shinjuku–ku, Tokyo<br />

163–0811 (JP).<br />

(for all designated States except / pour tous les États<br />

désignés sauf US)<br />

(72, 75) UCHIYAMA, Kenji [JP/JP]; Seiko Epson<br />

Corporation, 3–5, Owa 3–chome, Suwa–shi, Nagano–ken<br />

392–8502 (JP).<br />

(74) SUZUKI, Kisaburo et al. / etc.; Seiko Epson<br />

Corporation, <strong>Intellectual</strong> <strong>Property</strong> Dept., 3–5, Owa<br />

3–chome, Suwa–shi, Nagano–ken 392–8502 (JP).<br />

(81) CN JP KR US.<br />

(11) WO 98/48456 (13) A1<br />

(21) <strong>PCT</strong>/US98/08098<br />

(22) 22 Apr/avr <strong>1998</strong> (22.04.<strong>1998</strong>)<br />

(25) en (26) en<br />

(31) 60/044,008 (32) 24 Apr/avr 1997<br />

(24.04.1997)<br />

(33) US<br />

(<strong>43</strong>) 29 Oct/oct <strong>1998</strong> (29.10.<strong>1998</strong>)<br />

(51) 6 H01L 21/768, 21/311<br />

(54) • NANOWIRE ARRAYS<br />

• MATRICES DE NANOFILS<br />

(71) MASSACHUSETTS INSTITUTE OF<br />

TECHNOLOGY [US/US]; 77 Massachusetts<br />

Avenue, Cambridge, MA 02139 (US).<br />

(72) YING, Jackie, Y.; 9 Fairlane Terrace, Winchester,<br />

MA 01890 (US). ZHANG, Zhibo; Apartment<br />

#1, 3 Prentiss Street, Cambridge, MA 02140 (US).<br />

ZHANG, Lei; Room 205, 350 Memorial Drive,<br />

Cambridge, MA 02139 (US). DRESSELHAUS,<br />

Mildred, S.; 147 Jason Street, Arlington, MA<br />

02176 (US).<br />

(74) DALY, Christopher, S. et al. / etc.; Nutter,<br />

McClennen & Fish, LLP, One International Place,<br />

Boston, MA 02110 (US).<br />

(81) CA JP; EP (AT BE CH CY DE DK ES FI FR GB<br />

GR IE IT LU MC NL PT SE).<br />

(11) WO 98/48457 (13) A1<br />

(21) <strong>PCT</strong>/US98/05516<br />

(22) 19 Mar/mar <strong>1998</strong> (19.03.<strong>1998</strong>)<br />

(25) en (26) en<br />

(31) 08/844,924 (32) 21 Apr/avr 1997<br />

(21.04.1997)<br />

(33) US<br />

(<strong>43</strong>) 29 Oct/oct <strong>1998</strong> (29.10.<strong>1998</strong>)<br />

(51) 6 H01L 21/8238<br />

(54) • METHOD OF MAKING NMOS AND PMOS<br />

DEVICES WITH REDUCED MASKING<br />

STEPS<br />

• PROCEDE DE FABRICATION DE DISPOSI-<br />

TIFS NMOS ET PMOS NECESSITANT UN<br />

NOMBRE REDUIT D’ETAPES DE MAS-<br />

QUAGE<br />

(71) ADVANCED MICRO DEVICES, INC. [US/US];<br />

One AMD Place, Mail Stop 68, Sunnyvale, CA<br />

94088–3453 (US).<br />

(72) HAUSE, Frederick, N.; 4702 Circle Oak Cove,<br />

Austin, TX 78749 (US). DAWSON, Robert;<br />

3504 Beartree Circle, Austin, TX 78730 (US).<br />

FULFORD, H., Jim; 9808 Woodshire Drive,<br />

Austin, TX 78748 (US). GARDNER, Mark,<br />

I.; Highway 535, P.O. Box 249, Cedar Creek,<br />

TX 78612 (US). MICHAEL, Mark, W.; 1805<br />

Dayflower Trace, Cedar Park, TX 78613 (US).<br />

MOORE, Bradley, T.; 1502 Johnny Miller Trail,<br />

Austin, TX 78746 (US). WRISTERS, Derick, J.;<br />

1904 Terish Cover, Austin, TX 78728 (US).<br />

(74) DRAKE, Paul, S.; Advanced Micro Devices, Inc.,<br />

5204 East Ben White Boulevard, M/S 562, Austin,<br />

TX 78741 (US).<br />

(81) JP KR; EP (AT BE CH DE DK ES FI FR GB GR<br />

IE IT LU MC NL PT SE).<br />

(11) WO 98/48458 (13) A1<br />

(21) <strong>PCT</strong>/US98/08112<br />

(22) 20 Apr/avr <strong>1998</strong> (20.04.<strong>1998</strong>)<br />

(25) en (26) en<br />

(31) 08/837,685 (32) 21 Apr/avr 1997 (33) US<br />

(21.04.1997)<br />

(<strong>43</strong>) 29 Oct/oct <strong>1998</strong> (29.10.<strong>1998</strong>)<br />

(51) 6 H01L 23/48, 23/52, 29/40<br />

(54) • BALL GRID ARRAY PACKAGE EM-<br />

PLOYING SOLID CORE SOLDER BALLS<br />

• BOITIER A MATRICE DE GRILLE UTILI-<br />

SANT DES BILLES DE SOUDURE A NOYAU<br />

SOLIDE<br />

(71) LSI LOGIC CORPORATION [US/US]; 1551<br />

McCarthy Boulevard, Milpitas, CA 95035 (US).<br />

(for all designated States except / pour tous les États<br />

désignés sauf US)<br />

(72, 75) CHIA, Chok, J. [MY/US]; 10132 Prado Vista<br />

Drive, Cupertino, CA 95014 (US). VARIOT, Patrick<br />

[FR/US]; 2445 Westgate Avenue, San Jose,<br />

CA 95125 (US). ALAGARATNAM, Maniam<br />

[US/US]; 10424 Dempster Avenue, Cupertino, CA<br />

95014 (US).<br />

(74) WOODWARD, Henry, K. et al. / etc.; Townsend<br />

and Townsend and Crew LLP, 8th floor, Two Embarcadero<br />

Center, San Francisco, CA 94111–3834<br />

(US).<br />

(81) AL AM AT AU AZ BA BB BG BR BY CA CH<br />

CN CU CZ DE DK EE ES FI GB GE GH GM GW<br />

HU ID IL IS JP KE KG KP KR KZ LC LK LR<br />

LS LT LU LV MD MG MK MN MW MX NO NZ<br />

PL PT RO RU SD SE SG SI SK SL TJ TM TR<br />

TT UA UG US UZ VN YU ZW; AP (GH GM KE<br />

LS MW SD SZ UG ZW); EA (AM AZ BY KG<br />

KZ MD RU TJ TM); EP (AT BE CH CY DE DK<br />

ES FI FR GB GR IE IT LU MC NL PT SE); OA<br />

(BF BJ CF CG CI CM GA GN ML MR NE SN<br />

TD TG).<br />

(11) WO 98/48459 (13) A1<br />

(21) <strong>PCT</strong>/DE98/00769<br />

(22) 13 Mar/mar <strong>1998</strong> (13.03.<strong>1998</strong>)<br />

(25) de (26) de<br />

(31) 197 16 102.2 (32) 17 Apr/avr 1997 (33) DE<br />

(17.04.1997)<br />

(<strong>43</strong>) 29 Oct/oct <strong>1998</strong> (29.10.<strong>1998</strong>)<br />

(51) 6 H01L 23/60, 27/06<br />

(54) • INTEGRATED CIRCUIT WITH SEVERAL<br />

COMPONENTS AND METHOD FOR THE<br />

PRODUCTION THEREOF<br />

• CIRCUIT INTEGRE A PLUSIEURS COMPO-<br />

SANTS ET SON PROCEDE DE PRODUC-<br />

TION<br />

(71) SIEMENS AKTIENGESELLSCHAFT<br />

[DE/DE]; Wittelsbacher Platz 2, D–80333<br />

München (DE).<br />

(for all designated States except / pour tous les États<br />

désignés sauf US)<br />

(72, 75) ANTHOFER, Anton [DE/DE]; Böcklmühle<br />

26, D–92271 Freihung (DE). HÜBNER, Holger<br />

[DE/DE]; Hamsterweg 10, D–85598 Baldham<br />

(DE).<br />

(81) JP KR US; EP (AT BE CH DE DK ES FI FR GB<br />

GR IE IT LU MC NL PT SE).<br />

Published / Publiée : (c)<br />

(11) WO 98/48460<br />

(21) <strong>PCT</strong>/US98/07945<br />

(13) A1<br />

(22) 20 Apr/avr <strong>1998</strong> (20.04.<strong>1998</strong>)<br />

(25) en (26) en<br />

(31) 08/842,230 (32) 22 Apr/avr 1997<br />

(22.04.1997)<br />

(33) US<br />

(<strong>43</strong>) 29 Oct/oct <strong>1998</strong> (29.10.<strong>1998</strong>)<br />

(51) 6 H01L 27/108<br />

(54) • MEMORY INTEGRATED CIRCUITRY<br />

• CIRCUIT INTEGRE DE MEMOIRE<br />

(71) MICRON TECHNOLOGY, INC. [US/US]; 8000<br />

South Federal Way, Boise, ID 83706–9632 (US).<br />

(72) TRAN, Luan, C.; 1125 W. Sandy Court, Meridian,<br />

ID 83652 (US). REINBERG, Alan, R.; 1910 Lake<br />

Heron Lane, Boise, ID 83706 (US).<br />

(74) MATKIN, Mark, S. et al. / etc.; Wells, St. John,<br />

Roberts, Gregory & Matkin, P.S., W. 601 First<br />

Avenue #1300, Spokane, WA 99201–3817 (US).<br />

(81) AL AM AT AU AZ BA BB BG BR BY CA CH<br />

CN CU CZ DE DK EE ES FI GB GE GH GM<br />

GW HU ID IL IS JP KE KG KP KR KZ LC LK<br />

LR LS LT LU LV MD MG MK MN MW MX NO<br />

NZ PL PT RO RU SD SE SG SI SK SL TJ TM<br />

TR TT UA UG UZ VN YU ZW; AP (GH GM KE<br />

LS MW SD SZ UG ZW); EA (AM AZ BY KG<br />

KZ MD RU TJ TM); EP (AT BE CH CY DE DK<br />

ES FI FR GB GR IE IT LU MC NL PT SE); OA<br />

(BF BJ CF CG CI CM GA GN ML MR NE SN<br />

TD TG).<br />

Published / Publiée : (c)<br />

(11) WO 98/48461<br />

(21) <strong>PCT</strong>/US98/06873<br />

(13) A1<br />

(22) 9 Apr/avr <strong>1998</strong> (09.04.<strong>1998</strong>)<br />

(25) en (26) en<br />

(31) 08/844,536 (32) 18 Apr/avr 1997<br />

(18.04.1997)<br />

(33) US<br />

(<strong>43</strong>) 29 Oct/oct <strong>1998</strong> (29.10.<strong>1998</strong>)<br />

(51) 6 H01L 31/0203, 23/10, G11C 16/00<br />

(54) • INTEGRATED CIRCUIT PACKAGE<br />

• BOITIER DE MICROCIRCUIT