i A PHYSICAL IMPLEMENTATION WITH CUSTOM LOW POWER ...

i A PHYSICAL IMPLEMENTATION WITH CUSTOM LOW POWER ...

i A PHYSICAL IMPLEMENTATION WITH CUSTOM LOW POWER ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

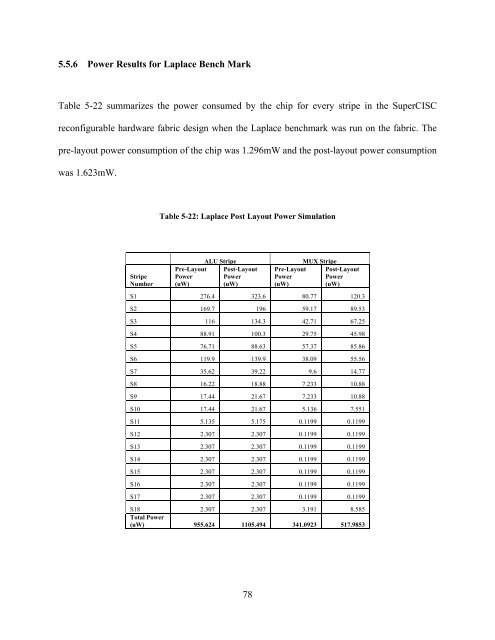

5.5.6 Power Results for Laplace Bench Mark<br />

Table 5-22 summarizes the power consumed by the chip for every stripe in the SuperCISC<br />

reconfigurable hardware fabric design when the Laplace benchmark was run on the fabric. The<br />

pre-layout power consumption of the chip was 1.296mW and the post-layout power consumption<br />

was 1.623mW.<br />

Table 5-22: Laplace Post Layout Power Simulation<br />

ALU Stripe MUX Stripe<br />

Pre-Layout Post-Layout Pre-Layout Post-Layout<br />

Stripe Power Power<br />

Power<br />

Power<br />

Number (uW) (uW) (uW)<br />

(uW)<br />

S1 276.4 323.6 80.77 120.3<br />

S2 169.7 196 59.17 89.53<br />

S3 116 134.3 42.71 67.25<br />

S4 88.91 100.3 29.75 45.98<br />

S5 76.71 88.63 57.37 85.86<br />

S6 119.9 139.9 38.09 55.56<br />

S7 35.62 39.22 9.6 14.77<br />

S8 16.22 18.88 7.233 10.88<br />

S9 17.44 21.67 7.233 10.88<br />

S10 17.44 21.67 5.136 7.551<br />

S11 5.135 5.175 0.1199 0.1199<br />

S12 2.307 2.307 0.1199 0.1199<br />

S13 2.307 2.307 0.1199 0.1199<br />

S14 2.307 2.307 0.1199 0.1199<br />

S15 2.307 2.307 0.1199 0.1199<br />

S16 2.307 2.307 0.1199 0.1199<br />

S17 2.307 2.307 0.1199 0.1199<br />

S18 2.307 2.307 3.191 8.585<br />

Total Power<br />

(uW) 955.624 1105.494 341.0923 517.9853<br />

78