2Gb: x4, x8, x16 DDR3 SDRAM - Micron

2Gb: x4, x8, x16 DDR3 SDRAM - Micron

2Gb: x4, x8, x16 DDR3 SDRAM - Micron

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>2Gb</strong>: <strong>x4</strong>, <strong>x8</strong>, <strong>x16</strong> <strong>DDR3</strong> <strong>SDRAM</strong><br />

Features<br />

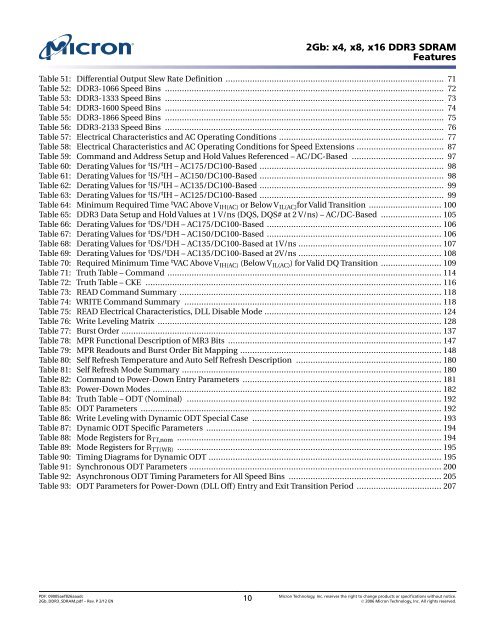

Table 51: Differential Output Slew Rate Definition .......................................................................................... 71<br />

Table 52: <strong>DDR3</strong>-1066 Speed Bins ................................................................................................................... 72<br />

Table 53: <strong>DDR3</strong>-1333 Speed Bins ................................................................................................................... 73<br />

Table 54: <strong>DDR3</strong>-1600 Speed Bins ................................................................................................................... 74<br />

Table 55: <strong>DDR3</strong>-1866 Speed Bins ................................................................................................................... 75<br />

Table 56: <strong>DDR3</strong>-2133 Speed Bins ................................................................................................................... 76<br />

Table 57: Electrical Characteristics and AC Operating Conditions .................................................................... 77<br />

Table 58: Electrical Characteristics and AC Operating Conditions for Speed Extensions .................................... 87<br />

Table 59: Command and Address Setup and Hold Values Referenced – AC/DC-Based ...................................... 97<br />

Table 60: Derating Values for t IS/ t IH – AC175/DC100-Based ............................................................................ 98<br />

Table 61: Derating Values for t IS/ t IH – AC150/DC100-Based ............................................................................ 98<br />

Table 62: Derating Values for t IS/ t IH – AC135/DC100-Based ............................................................................ 99<br />

Table 63: Derating Values for t IS/ t IH – AC125/DC100-Based ............................................................................ 99<br />

Table 64: Minimum Required Time t VAC Above V IH(AC) or Below V IL(AC)for Valid Transition .............................. 100<br />

Table 65: <strong>DDR3</strong> Data Setup and Hold Values at 1 V/ns (DQS, DQS# at 2 V/ns) – AC/DC-Based ......................... 105<br />

Table 66: Derating Values for t DS/ t DH – AC175/DC100-Based ........................................................................ 106<br />

Table 67: Derating Values for t DS/ t DH – AC150/DC100-Based ........................................................................ 106<br />

Table 68: Derating Values for t DS/ t DH – AC135/DC100-Based at 1V/ns ........................................................... 107<br />

Table 69: Derating Values for t DS/ t DH – AC135/DC100-Based at 2V/ns ........................................................... 108<br />

Table 70: Required Minimum Time t VAC Above V IH(AC) (Below V IL(AC)) for Valid DQ Transition ......................... 109<br />

Table 71: Truth Table – Command ................................................................................................................. 114<br />

Table 72: Truth Table – CKE .......................................................................................................................... 116<br />

Table 73: READ Command Summary ............................................................................................................ 118<br />

Table 74: WRITE Command Summary .......................................................................................................... 118<br />

Table 75: READ Electrical Characteristics, DLL Disable Mode ......................................................................... 124<br />

Table 76: Write Leveling Matrix ..................................................................................................................... 128<br />

Table 77: Burst Order .................................................................................................................................... 137<br />

Table 78: MPR Functional Description of MR3 Bits ........................................................................................ 147<br />

Table 79: MPR Readouts and Burst Order Bit Mapping ................................................................................... 148<br />

Table 80: Self Refresh Temperature and Auto Self Refresh Description ............................................................ 180<br />

Table 81: Self Refresh Mode Summary ........................................................................................................... 180<br />

Table 82: Command to Power-Down Entry Parameters .................................................................................. 181<br />

Table 83: Power-Down Modes ....................................................................................................................... 182<br />

Table 84: Truth Table – ODT (Nominal) ......................................................................................................... 192<br />

Table 85: ODT Parameters ............................................................................................................................ 192<br />

Table 86: Write Leveling with Dynamic ODT Special Case .............................................................................. 193<br />

Table 87: Dynamic ODT Specific Parameters ................................................................................................. 194<br />

Table 88: Mode Registers for R TT,nom ............................................................................................................. 194<br />

Table 89: Mode Registers for R TT(WR) ............................................................................................................. 195<br />

Table 90: Timing Diagrams for Dynamic ODT ................................................................................................ 195<br />

Table 91: Synchronous ODT Parameters ........................................................................................................ 200<br />

Table 92: Asynchronous ODT Timing Parameters for All Speed Bins ............................................................... 205<br />

Table 93: ODT Parameters for Power-Down (DLL Off) Entry and Exit Transition Period ................................... 207<br />

PDF: 09005aef826aaadc<br />

<strong>2Gb</strong>_<strong>DDR3</strong>_<strong>SDRAM</strong>.pdf – Rev. P 2/12 EN 10 <strong>Micron</strong> Technology, Inc. reserves the right to change products or specifications without notice.<br />

� 2006 <strong>Micron</strong> Technology, Inc. All rights reserved.