2Gb: x4, x8, x16 DDR3 SDRAM - Micron

2Gb: x4, x8, x16 DDR3 SDRAM - Micron

2Gb: x4, x8, x16 DDR3 SDRAM - Micron

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

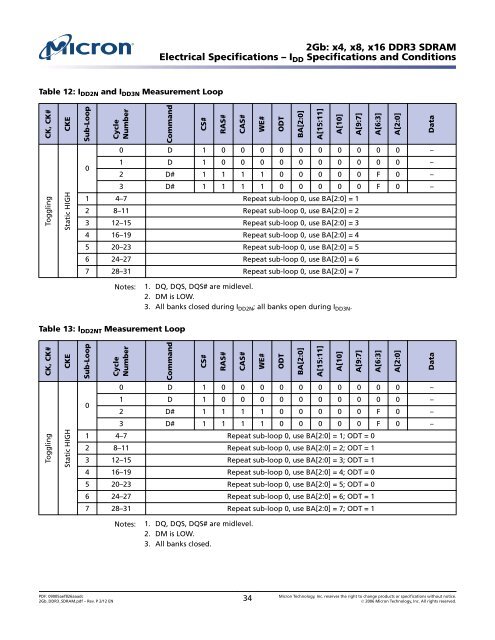

Table 12: I DD2N and I DD3N Measurement Loop<br />

CK, CK#<br />

Toggling<br />

CKE<br />

Static HIGH<br />

Sub-Loop<br />

Cycle<br />

Number<br />

Command<br />

CS#<br />

RAS#<br />

CAS#<br />

WE#<br />

0 D 1 0 0 0 0 0 0 0 0 0 0 –<br />

0<br />

1<br />

2<br />

D<br />

D#<br />

1<br />

1<br />

0<br />

1<br />

0<br />

1<br />

0<br />

1<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

F<br />

0<br />

0<br />

–<br />

–<br />

3 D# 1 1 1 1 0 0 0 0 0 F 0 –<br />

1 4–7 Repeat sub-loop 0, use BA[2:0] = 1<br />

2 8–11 Repeat sub-loop 0, use BA[2:0] = 2<br />

3 12–15 Repeat sub-loop 0, use BA[2:0] = 3<br />

4 16–19 Repeat sub-loop 0, use BA[2:0] = 4<br />

5 20–23 Repeat sub-loop 0, use BA[2:0] = 5<br />

6 24–27 Repeat sub-loop 0, use BA[2:0] = 6<br />

7 28–31 Repeat sub-loop 0, use BA[2:0] = 7<br />

Table 13: I DD2NT Measurement Loop<br />

CK, CK#<br />

Toggling<br />

CKE<br />

Static HIGH<br />

Sub-Loop<br />

Notes: 1. DQ, DQS, DQS# are midlevel.<br />

2. DM is LOW.<br />

3. All banks closed during I DD2N; all banks open during I DD3N.<br />

Cycle<br />

Number<br />

<strong>2Gb</strong>: <strong>x4</strong>, <strong>x8</strong>, <strong>x16</strong> <strong>DDR3</strong> <strong>SDRAM</strong><br />

Electrical Specifications – I DD Specifications and Conditions<br />

Command<br />

CS#<br />

RAS#<br />

CAS#<br />

WE#<br />

0 D 1 0 0 0 0 0 0 0 0 0 0 –<br />

0<br />

1<br />

2<br />

D<br />

D#<br />

1<br />

1<br />

0<br />

1<br />

0<br />

1<br />

0<br />

1<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

F<br />

0<br />

0<br />

–<br />

–<br />

3 D# 1 1 1 1 0 0 0 0 0 F 0 –<br />

1 4–7 Repeat sub-loop 0, use BA[2:0] = 1; ODT = 0<br />

2 8–11 Repeat sub-loop 0, use BA[2:0] = 2; ODT = 1<br />

3 12–15 Repeat sub-loop 0, use BA[2:0] = 3; ODT = 1<br />

4 16–19 Repeat sub-loop 0, use BA[2:0] = 4; ODT = 0<br />

5 20–23 Repeat sub-loop 0, use BA[2:0] = 5; ODT = 0<br />

6 24–27 Repeat sub-loop 0, use BA[2:0] = 6; ODT = 1<br />

7 28–31 Repeat sub-loop 0, use BA[2:0] = 7; ODT = 1<br />

Notes: 1. DQ, DQS, DQS# are midlevel.<br />

2. DM is LOW.<br />

3. All banks closed.<br />

PDF: 09005aef826aaadc<br />

<strong>2Gb</strong>_<strong>DDR3</strong>_<strong>SDRAM</strong>.pdf – Rev. P 2/12 EN 34 <strong>Micron</strong> Technology, Inc. reserves the right to change products or specifications without notice.<br />

� 2006 <strong>Micron</strong> Technology, Inc. All rights reserved.<br />

ODT<br />

ODT<br />

BA[2:0]<br />

BA[2:0]<br />

A[15:11]<br />

A[15:11]<br />

A[10]<br />

A[10]<br />

A[9:7]<br />

A[9:7]<br />

A[6:3]<br />

A[6:3]<br />

A[2:0]<br />

A[2:0]<br />

Data<br />

Data