2Gb: x4, x8, x16 DDR3 SDRAM - Micron

2Gb: x4, x8, x16 DDR3 SDRAM - Micron

2Gb: x4, x8, x16 DDR3 SDRAM - Micron

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

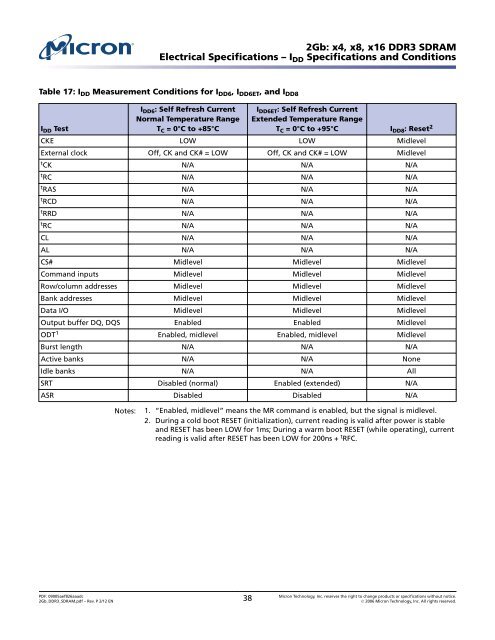

<strong>2Gb</strong>: <strong>x4</strong>, <strong>x8</strong>, <strong>x16</strong> <strong>DDR3</strong> <strong>SDRAM</strong><br />

Electrical Specifications – I DD Specifications and Conditions<br />

Table 17: I DD Measurement Conditions for I DD6, I DD6ET, and I DD8<br />

IDD6: Self Refresh Current IDD6ET: Self Refresh Current<br />

Normal Temperature Range Extended Temperature Range<br />

IDD Test<br />

TC = 0°C to +85°C<br />

TC = 0°C to +95°C IDD8: Reset2 CKE LOW LOW Midlevel<br />

External clock Off, CK and CK# = LOW Off, CK and CK# = LOW Midlevel<br />

tCK N/A N/A N/A<br />

tRC N/A N/A N/A<br />

tRAS N/A N/A N/A<br />

tRCD N/A N/A N/A<br />

tRRD N/A N/A N/A<br />

tRC N/A N/A N/A<br />

CL N/A N/A N/A<br />

AL N/A N/A N/A<br />

CS# Midlevel Midlevel Midlevel<br />

Command inputs Midlevel Midlevel Midlevel<br />

Row/column addresses Midlevel Midlevel Midlevel<br />

Bank addresses Midlevel Midlevel Midlevel<br />

Data I/O Midlevel Midlevel Midlevel<br />

Output buffer DQ, DQS Enabled Enabled Midlevel<br />

ODT1 Enabled, midlevel Enabled, midlevel Midlevel<br />

Burst length N/A N/A N/A<br />

Active banks N/A N/A None<br />

Idle banks N/A N/A All<br />

SRT Disabled (normal) Enabled (extended) N/A<br />

ASR Disabled Disabled N/A<br />

Notes: 1. “Enabled, midlevel” means the MR command is enabled, but the signal is midlevel.<br />

2. During a cold boot RESET (initialization), current reading is valid after power is stable<br />

and RESET has been LOW for 1ms; During a warm boot RESET (while operating), current<br />

reading is valid after RESET has been LOW for 200ns + t RFC.<br />

PDF: 09005aef826aaadc<br />

<strong>2Gb</strong>_<strong>DDR3</strong>_<strong>SDRAM</strong>.pdf – Rev. P 2/12 EN 38 <strong>Micron</strong> Technology, Inc. reserves the right to change products or specifications without notice.<br />

� 2006 <strong>Micron</strong> Technology, Inc. All rights reserved.