- Page 1 and 2:

POLITECHNIKA GDAŃSKA Pakiet inform

- Page 3 and 4:

1. Opis Wydziału Wydział Elektron

- Page 5 and 6:

1.2. Władze Wydziału Dziekan prof

- Page 7 and 8:

e-mail: ksa@eti.pg.gda.pl WWW: http

- Page 9 and 10:

Inf + EiT + AiR EiT + AiR Automatyk

- Page 11 and 12:

1.5.4. Studia doktoranckie stacjona

- Page 13 and 14:

Semestr 3 kierunek AUTOMATYKA i ROB

- Page 15 and 16:

Semestr 8 kierunek AUTOMATYKA i ROB

- Page 17 and 18:

Specjalność: Komputerowe systemy

- Page 19 and 20:

2.2.1. Elektronika i telekomunikacj

- Page 21 and 22:

Specjalność: Inżynieria komunika

- Page 23 and 24:

2.2.2. Elektronika i telekomunikacj

- Page 25 and 26:

Specjalność: Inżynieria dźwięk

- Page 27 and 28:

2.3. Informatyka Semestr 1 kierunek

- Page 29 and 30:

Semestr 8 kierunek INFORMATYKA g/ty

- Page 31 and 32:

Specjalność: Modelowanie i progra

- Page 33 and 34:

3. Treści przedmiotów W tym rozdz

- Page 35 and 36:

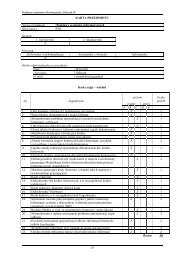

Lp. Zagadnienie poziom wiedzy umiej

- Page 37 and 38:

prostej. Macierze i przekształceni

- Page 39 and 40:

18. Monotniczność i extrema funkc

- Page 41 and 42:

9. Warunek konieczny istnienia ekst

- Page 43 and 44:

Nazwa przedmiotu Analiza matematycz

- Page 45 and 46:

Nazwa przedmiotu Architektura kompu

- Page 47 and 48:

52. Komputery CISC i RISC, sterowan

- Page 49 and 50:

Nazwa przedmiotu Automaty i języki

- Page 51 and 52:

Nazwa przedmiotu Badania operacyjne

- Page 53 and 54:

Nazwa przedmiotu Bazy danych Skrót

- Page 55 and 56:

Nazwa przedmiotu Bazy danych Skrót

- Page 57 and 58:

KARTA PRZEDMIOTU Nazwa przedmiotu C

- Page 59 and 60:

Nazwa przedmiotu Elektrodynamika Sk

- Page 61 and 62:

KARTA PRZEDMIOTU Nazwa przedmiotu E

- Page 63 and 64:

Nazwa przedmiotu Filtry cyfrowe Skr

- Page 65 and 66:

Przemiany gazu doskonałego 23. Ró

- Page 67 and 68:

6. Zadania z dynamiki ruchu postęp

- Page 69 and 70:

Nazwa przedmiotu Fizyka Skrót nazw

- Page 71 and 72:

2. układzie odniesienia Zadania z

- Page 73 and 74:

24. Ścienianie kształtu - definic

- Page 75 and 76:

KARTA PRZEDMIOTU Nazwa przedmiotu H

- Page 77 and 78:

Nazwa przedmiotu Identyfikacja proc

- Page 79 and 80:

KARTA PRZEDMIOTU Nazwa przedmiotu I

- Page 81 and 82:

KARTA PRZEDMIOTU Nazwa przedmiotu I

- Page 83 and 84:

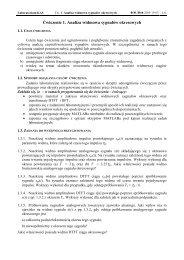

Karta zajęć - laboratorium poziom

- Page 85 and 86:

Karta zajęć - laboratorium poziom

- Page 87 and 88:

15. Mikrofalowe układy monolityczn

- Page 89 and 90:

33. Nieklasyczne cykle życia: mode

- Page 91 and 92:

39. Formułowanie jakościowych reg

- Page 93 and 94:

30. Kolokwium sprawdzające - obiek

- Page 95 and 96:

Karta zajęć - projekt poziom licz

- Page 97 and 98:

36. Maszyny stanów. X X 1 37. Dete

- Page 99 and 100:

przeprowadzane w miejscu ich instal

- Page 101 and 102:

Lp. Zagadnienie Karta zajęć - ćw

- Page 103 and 104:

zasada działania, przebiegi prąd

- Page 105 and 106:

Nazwa przedmiotu Kultura języka po

- Page 107 and 108:

Nazwa przedmiotu Skrót nazwy Logik

- Page 109 and 110:

Nazwa przedmiotu Matematyka dyskret

- Page 111 and 112:

Nazwa przedmiotu Mechanika Skrót n

- Page 113 and 114:

KARTA PRZEDMIOTU Nazwa przedmiotu M

- Page 115 and 116:

Karta zajęć - laboratorium poziom

- Page 117 and 118:

Nazwa przedmiotu Metody numeryczne

- Page 119 and 120:

Nazwa przedmiotu Metody probabilist

- Page 121 and 122:

17. Wyznaczanie rozkładów brzegow

- Page 123 and 124:

30. Zastosowania metod przetwarzani

- Page 125 and 126:

KARTA PRZEDMIOTU Nazwa przedmiotu M

- Page 127 and 128:

programie Power Logic, m. in. listy

- Page 129 and 130:

wielkości nieelektrycznych 28. Met

- Page 131 and 132:

Karta zajęć - laboratorium poziom

- Page 133 and 134:

28. Metody pomiarowe parametrów im

- Page 135 and 136:

30. Rozwiązania interfejsów SPI w

- Page 137 and 138:

PIC16F877 29. Interfejs SPI X 0,33

- Page 139 and 140:

Nazwa przedmiotu Multimedia i inter

- Page 141 and 142:

2. bezpamięciowych Obliczanie wyda

- Page 143 and 144:

KARTA PRZEDMIOTU Nazwa przedmiotu O

- Page 145 and 146:

KARTA PRZEDMIOTU Nazwa przedmiotu O

- Page 147 and 148:

KARTA PRZEDMIOTU Nazwa przedmiotu O

- Page 149 and 150:

Nazwa przedmiotu Optoelektronika Sk

- Page 151 and 152:

Nazwa przedmiotu Podstawy automatyk

- Page 153 and 154:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 155 and 156:

zwrotnego (PLL). 29. Podstawowe rod

- Page 157 and 158:

ównoległe systemów dyskretnych,

- Page 159 and 160:

10. DTFT - widma sygnałów dyskret

- Page 161 and 162:

9. Określanie pojemności systemu

- Page 163 and 164:

a. bipolarnych X 1 33. b. nMOS X 0.

- Page 165 and 166:

2. Obliczanie wydajności informacy

- Page 167 and 168:

poziom liczba Lp. Zagadnienie wiedz

- Page 169 and 170:

Nazwa przedmiotu Podstawy robotyki

- Page 171 and 172:

Karta zajęć - laboratorium poziom

- Page 173 and 174:

Nazwa przedmiotu Podstawy teorii ob

- Page 175 and 176:

Nazwa przedmiotu Praktyka programow

- Page 177 and 178:

Nazwa przedmiotu Procesory sygnało

- Page 179 and 180:

charakterystyce. 5. Rrealizacja fil

- Page 181 and 182:

19. Biały szum, pasmowy biały szu

- Page 183 and 184:

Lp. Zagadnienie 1. Przygotowanie i

- Page 185 and 186:

5. VHDL. Synteza, implementacja, sy

- Page 187 and 188:

35. Korzystanie z baz danych z pozi

- Page 189 and 190:

28. Problem drzew spinających w gr

- Page 191 and 192:

30. Modelowanie obciążenia sieci

- Page 193 and 194:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 195 and 196:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 197 and 198:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 199 and 200:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 201 and 202:

KARTA PRZEDMIOTU Nazwa przedmiotu R

- Page 203 and 204:

egresji. 27. Liniowa predykcja śre

- Page 205 and 206:

KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 207 and 208:

5. Sieci bezprzewodowe - konfigurac

- Page 209 and 210:

Lp. Zagadnienie Karta zajęć - lab

- Page 211 and 212:

podstawowych funkcji sieci telekomu

- Page 213 and 214:

Nazwa przedmiotu Sterowanie analogo

- Page 215 and 216:

Nazwa przedmiotu Struktury baz dany

- Page 217 and 218:

Lp. Zagadnienie Karta zajęć - lab

- Page 219 and 220:

określających dostępność miejs

- Page 221 and 222:

34. Metody zobrazowania sygnałów

- Page 223 and 224:

odzaju kanałów transmisyjnych. Te

- Page 225 and 226:

13. Mikrokontroler AVR ćw. B. X 2

- Page 227 and 228:

Nazwa przedmiotu Systemy multimedia

- Page 229 and 230:

Nazwa przedmiotu Systemy nawigacyjn

- Page 231 and 232:

Nazwa przedmiotu Systemy operacyjne

- Page 233 and 234:

KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 235 and 236:

Nazwa przedmiotu Systemy rozproszon

- Page 237 and 238:

KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 239 and 240:

Nazwa przedmiotu Systemy telekomuni

- Page 241 and 242:

KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 243 and 244:

A B C D E 1. Wprowadzenie do język

- Page 245 and 246:

31. Analiza liniowych obwodów anal

- Page 247 and 248:

Nazwa przedmiotu Technika antenowa

- Page 249 and 250:

Lp. Zagadnienie Karta zajęć - lab

- Page 251 and 252:

21. Synteza układów sekwencyjnych

- Page 253 and 254:

Razem 30 253

- Page 255 and 256:

UWAGA: każda grupa laboratoryjna w

- Page 257 and 258:

7. Pomiar wymiarów szczelin i prze

- Page 259 and 260:

3. Procedury obsługi wyświetlacza

- Page 261 and 262:

5. Procedury obsługi klawiatury i

- Page 263 and 264:

Karta zajęć - laboratorium poziom

- Page 265 and 266:

Lp. Zagadnienie Karta zajęć - lab

- Page 267 and 268:

29. Kierunki rozwoju techniki świa

- Page 269 and 270:

KARTA PRZEDMIOTU Nazwa przedmiotu T

- Page 271 and 272:

KARTA PRZEDMIOTU Nazwa przedmiotu T

- Page 273 and 274:

Nazwa przedmiotu Teoria sterowania

- Page 275 and 276:

28. Systemy bez oraz z cyklem uczen

- Page 277 and 278:

29. Upraszczanie struktury układu

- Page 279 and 280:

24. Podstawy teoretyczne metod synt

- Page 281 and 282:

Nazwa przedmiotu Układy mikrofalow

- Page 283 and 284:

KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 285 and 286:

KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 287 and 288:

KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 289 and 290:

3.2. Przedmioty specjalnościowe 3.

- Page 291 and 292:

Nazwa przedmiotu Aplikacje Microsof

- Page 293 and 294:

KARTA PRZEDMIOTU Nazwa przedmiotu B

- Page 295 and 296:

, ) 295

- Page 297 and 298:

8. Projekt ekonomiczny - specyfikac

- Page 299 and 300:

28. Powiadomienia (notifications) w

- Page 301 and 302:

Nazwa przedmiotu Internetowe usług

- Page 303 and 304:

KARTA PRZEDMIOTU Nazwa przedmiotu O

- Page 305 and 306:

poziom liczba Lp. Zagadnienie Wiedz

- Page 307 and 308:

Lp. Zagadnienie Karta zajęć - lab

- Page 309 and 310:

Lp. Zagadnienie poziom wiedzy umiej

- Page 311 and 312:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 313 and 314:

Nazwa przedmiotu Rozproszone bazy d

- Page 315 and 316:

3.2.2. Inteligentne systemy decyzyj

- Page 317 and 318:

KARTA PRZEDMIOTU Nazwa przedmiotu E

- Page 319 and 320:

Nazwa przedmiotu Inteligencja oblic

- Page 321 and 322:

KARTA PRZEDMIOTU Nazwa przedmiotu O

- Page 323 and 324:

2. rozwiązywania problemów OS i b

- Page 325 and 326:

25. Dualizm w programowaniu liniowy

- Page 327 and 328:

Lp. Zagadnienie Karta zajęć - sem

- Page 329 and 330:

Lp. Zagadnienie Karta zajęć - sem

- Page 331 and 332:

3.2.3. Inżynieria biomedyczna Nazw

- Page 333 and 334:

KARTA PRZEDMIOTU Nazwa przedmiotu G

- Page 335 and 336:

KARTA PRZEDMIOTU Nazwa przedmiotu H

- Page 337 and 338:

KARTA PRZEDMIOTU Nazwa przedmiotu M

- Page 339 and 340:

KARTA PRZEDMIOTU Nazwa przedmiotu M

- Page 341 and 342:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 343 and 344:

KARTA PRZEDMIOTU Nazwa przedmiotu R

- Page 345 and 346:

Nazwa przedmiotu Serwery aplikacji

- Page 347 and 348:

Lp. Zagadnienie poziom wiedzy umiej

- Page 349 and 350:

Nazwa przedmiotu Wykład monografic

- Page 351 and 352:

3.2.4. Inteligentne systemy interak

- Page 353 and 354:

Nazwa przedmiotu Dokumenty cyfrowe

- Page 355 and 356:

25. Przezroczystość bez uwzględn

- Page 357 and 358:

32. Bezstratne kodowanie predykcyjn

- Page 359 and 360:

KARTA PRZEDMIOTU Nazwa przedmiotu M

- Page 361 and 362:

Nazwa przedmiotu Skrót nazwy KARTA

- Page 363 and 364:

Lp. Zagadnienie Karta zajęć - lab

- Page 365 and 366:

23. Generacja cienia przy łączeni

- Page 367 and 368:

7. OpenGL - maska ekranu X 2 8. Ope

- Page 369 and 370:

35 Algorytmy doboru struktury sieci

- Page 371 and 372:

Lp. Zagadnienie poziom wiedzy umiej

- Page 373 and 374:

5. Obiekty rodzime i obce na scenie

- Page 375 and 376:

24. Wizualizacja dokumentów, zapyt

- Page 377 and 378:

35. Nadmiarowość informacyjna syg

- Page 379 and 380:

Lp. Zagadnienie Karta zajęć - pro

- Page 381 and 382:

Nazwa przedmiotu Ochrona przeciwdź

- Page 383 and 384:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 385 and 386:

Nazwa przedmiotu Podstawy elektroak

- Page 387 and 388:

Nazwa przedmiotu Pomiary elektroaku

- Page 389 and 390:

Nazwa przedmiotu Synteza dźwięku

- Page 391 and 392:

36. System ODEON X 0,67 37. System

- Page 393 and 394:

KARTA PRZEDMIOTU Nazwa przedmiotu T

- Page 395 and 396:

Nazwa przedmiotu Technologia nagra

- Page 397 and 398:

Nazwa przedmiotu Technologia nagra

- Page 399 and 400:

3.2.6. Inżynieria komunikacji bezp

- Page 401 and 402:

Nazwa przedmiotu CAD układów b.w.

- Page 403 and 404:

6. Macierz rozproszenia i projektow

- Page 405 and 406:

A B D E 1. Układy dopasowujące -

- Page 407 and 408:

11. Tranzystory polowe MESFET, HEMT

- Page 409 and 410:

Nazwa przedmiotu Fotonika Skrót na

- Page 411 and 412:

Nazwa przedmiotu Miernictwo mikrofa

- Page 413 and 414:

Nazwa przedmiotu Nowe technologie b

- Page 415 and 416:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 417 and 418:

Nazwa przedmiotu Sieci bezprzewodow

- Page 419 and 420:

15. Oscylatory tranzystorowe - wymu

- Page 421 and 422:

2. Transient) - wprowadzenie Analiz

- Page 423 and 424:

KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 425 and 426:

KARTA PRZEDMIOTU Nazwa przedmiotu B

- Page 427 and 428:

eguły asocjacyjne Razem !Błąd sk

- Page 429 and 430:

28 Inżynieria wymagań w świetle

- Page 431 and 432:

Nazwa przedmiotu Platformy technolo

- Page 433 and 434:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 435 and 436:

Nazwa przedmiotu Strategie informat

- Page 437 and 438:

Nazwa przedmiotu Systemy wbudowane

- Page 439 and 440:

Nazwa przedmiotu Wykłady monografi

- Page 441 and 442:

poziom liczba Lp. Zagadnienie wiedz

- Page 443 and 444:

KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 445 and 446:

7. Ograniczenia X 0,5 8. Wstępne p

- Page 447 and 448:

czujniki mikrofalowe, czujniki dual

- Page 449 and 450:

Nazwa przedmiotu Diagnostyka elektr

- Page 451 and 452:

IEEE 1149.1 X 1 9. Testowanie ukła

- Page 453 and 454:

programowe, debuggery, emulatory sp

- Page 455 and 456:

2. Modele filtru eliptycznego 7. rz

- Page 457 and 458:

33. Prognozowanie eksploatacyjnej n

- Page 459 and 460:

Lp. Zagadnienie Karta zajęć - lab

- Page 461 and 462:

sprzętu i oprogramowania systemów

- Page 463 and 464:

Karta zajęć - laboratorium poziom

- Page 465 and 466:

27. Spektroskopia impedancyna w sze

- Page 467 and 468:

Karta zajęć - projekt poziom licz

- Page 469 and 470:

użytkowe urządzeń wyświetlając

- Page 471 and 472:

poziom liczba Lp. Zagadnienie wiedz

- Page 473 and 474:

17. komunikacyjnych. Model odniesie

- Page 475 and 476:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 477 and 478:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 479 and 480:

Nazwa przedmiotu Roboty mobilne Skr

- Page 481 and 482:

Nazwa przedmiotu Sterowanie adaptac

- Page 483 and 484:

Nazwa przedmiotu Sterowanie optymal

- Page 485 and 486:

4. Metody poszukiwań prostych (alg

- Page 487 and 488:

24. Sterowanie wielkością produkc

- Page 489 and 490:

Nazwa przedmiotu Sterowanie stochas

- Page 491 and 492:

KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 493 and 494:

Karta zajęć - projekt poziom licz

- Page 495 and 496:

4. Opracowanie dwóch heurystyk dla

- Page 497 and 498:

Lp. Zagadnienie poziom wiedzy umiej

- Page 499 and 500:

KARTA PRZEDMIOTU Nazwa przedmiotu E

- Page 501 and 502:

3. Zaawansowane mechanizmy C# X 1 4

- Page 503 and 504:

6. Frameworki www 3 7. Realizacja G

- Page 505 and 506:

Nazwa przedmiotu Obliczenia kwantow

- Page 507 and 508:

10. Funkcje hashujące. X 1 11. Uzg

- Page 509 and 510:

Lp. Zagadnienie Karta zajęć - lab

- Page 511 and 512:

13. Programowanie i konfiguracja Cl

- Page 513 and 514:

Lp. Zagadnienie Karta zajęć - lab

- Page 515 and 516:

Nazwa przedmiotu Systemy z bazą wi

- Page 517 and 518:

KARTA PRZEDMIOTU Nazwa przedmiotu T

- Page 519 and 520:

KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 521 and 522:

3.2.11. Optoelektronika Nazwa przed

- Page 523 and 524:

KARTA PRZEDMIOTU Nazwa przedmiotu D

- Page 525 and 526:

KARTA PRZEDMIOTU Nazwa przedmiotu E

- Page 527 and 528:

KARTA PRZEDMIOTU Nazwa przedmiotu E

- Page 529 and 530:

Lp. Zagadnienie Karta zajęć - lab

- Page 531 and 532:

Karta zajęć - ćwiczenia poziom l

- Page 533 and 534:

Nazwa przedmiotu Podstawy fotoniki

- Page 535 and 536:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 537 and 538:

Lp. Zagadnienie poziom wiedzy umiej

- Page 539 and 540:

7. Pomiar wymiarów szczelin i prze

- Page 541 and 542:

9. Spektroskopia Cavity Ring-Down X

- Page 543 and 544:

wykorzystaniem wektora Stokesa. X 1

- Page 545 and 546:

3.2.12. Sieci komputerowe KARTA PRZ

- Page 547 and 548:

KARTA PRZEDMIOTU Nazwa przedmiotu M

- Page 549 and 550:

Nazwa przedmiotu Media komunikacyjn

- Page 551 and 552:

Nazwa przedmiotu Metody analizy STI

- Page 553 and 554:

KARTA PRZEDMIOTU Nazwa przedmiotu M

- Page 555 and 556:

KARTA PRZEDMIOTU Nazwa przedmiotu O

- Page 557 and 558:

ezprzewodowymi 37. Zasady wspólpra

- Page 559 and 560:

20. Architektura usług zróżnicow

- Page 561 and 562:

8. Usługi domenowe Windows i NDS N

- Page 563 and 564:

KARTA PRZEDMIOTU Nazwa przedmiotu W

- Page 565 and 566:

KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 567 and 568:

3.2.13. Systemy czasu rzeczywistego

- Page 569 and 570:

KARTA PRZEDMIOTU Nazwa przedmiotu A

- Page 571 and 572:

KARTA PRZEDMIOTU Nazwa przedmiotu D

- Page 573 and 574:

KARTA PRZEDMIOTU Nazwa przedmiotu L

- Page 575 and 576:

Karta zajęć - projekt poziom licz

- Page 577 and 578:

31. Wysokościomierz, czujniki zanu

- Page 579 and 580:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 581 and 582:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 583 and 584:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 585 and 586:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 587 and 588:

KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 589 and 590:

Razem 15 589

- Page 591 and 592:

Karta zajęć - projekt poziom licz

- Page 593 and 594:

KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 595 and 596: Karta zajęć - seminarium poziom l

- Page 597 and 598: wbudowanego. 2. Projekt koncepcyjny

- Page 599 and 600: 4. Mapy rastrowe i wektorowe. Osadz

- Page 601 and 602: 6. Testowanie systemu klasyfikując

- Page 603 and 604: wektorową do tworzenia map wektoro

- Page 605 and 606: 2. Metody projektowanie filtrów cy

- Page 607 and 608: określenie struktury systemu. 6. S

- Page 609 and 610: Nazwa przedmiotu Systemy geoinforma

- Page 611 and 612: 2. Proste analizy danych w GIS: two

- Page 613 and 614: 12. Implementacja węzłów wspomag

- Page 615 and 616: 6. Sposoby testowania systemów geo

- Page 617 and 618: 8. Tworzenie funkcji prezentującej

- Page 619 and 620: KARTA PRZEDMIOTU Nazwa przedmiotu A

- Page 621 and 622: Nazwa przedmiotu Kodowanie kanałow

- Page 623 and 624: Nazwa przedmiotu Kodowanie źródł

- Page 625 and 626: KARTA PRZEDMIOTU Nazwa przedmiotu M

- Page 627 and 628: 17. Dobór parametrów systemu OFDM

- Page 629 and 630: 7. Przewidywanie obszaru działania

- Page 631 and 632: Nazwa przedmiotu Systemy drugiej ge

- Page 633 and 634: 6. Modelowanie odpowiedzi impulsowe

- Page 635 and 636: KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 637 and 638: KARTA PRZEDMIOTU Nazwa przedmiotu T

- Page 639 and 640: KARTA PRZEDMIOTU Nazwa przedmiotu T

- Page 641 and 642: 8. Odrobienie zaległości X 2 Raze

- Page 643 and 644: 29. Synteza ścieżki danych i jedn

- Page 645: Karta zajęć - laboratorium poziom

- Page 649 and 650: poziom liczba Lp. Zagadnienie wiedz

- Page 651 and 652: Fast Ethernet. 3. Projekt układu r

- Page 653 and 654: Karta zajęć - laboratorium poziom

- Page 655 and 656: Lp. Zagadnienie Karta zajęć - sem

- Page 657 and 658: KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 659 and 660: KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 661 and 662: KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 663 and 664: 3.2.17. Systemy teleinformacyjne KA

- Page 665 and 666: KARTA PRZEDMIOTU Nazwa przedmiotu K

- Page 667 and 668: KARTA PRZEDMIOTU Nazwa przedmiotu N

- Page 669 and 670: Nazwa przedmiotu Pomiary w sieciach

- Page 671 and 672: KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 673 and 674: KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 675 and 676: KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 677 and 678: zasobów procesora na „pompę dan

- Page 679 and 680: optycznych, procedura tworzenia ram

- Page 681 and 682: Lp. Zagadnienie Karta zajęć - lab

- Page 683 and 684: 4. pakietu w każdym ruterze sieci.

- Page 685 and 686: 33. Struktury filtrów z maskowanie

- Page 687: KARTA PRZEDMIOTU Nazwa przedmiotu Z

![Wersja pełna [11,39 MB] - Wydział Elektroniki, Telekomunikacji i ...](https://img.yumpu.com/19534885/646/500x640/wersja-pelna-1139-mb-wydzial-elektroniki-telekomunikacji-i-.jpg)

![Wersja pełna [11,39 MB] - Wydział Elektroniki, Telekomunikacji i ...](https://img.yumpu.com/19534883/1/184x260/wersja-pelna-1139-mb-wydzial-elektroniki-telekomunikacji-i-.jpg?quality=85)

![Wersja pełna [10,99 MB] - Wydział Elektroniki, Telekomunikacji i ...](https://img.yumpu.com/19534878/1/184x260/wersja-pelna-1099-mb-wydzial-elektroniki-telekomunikacji-i-.jpg?quality=85)

![2cos( ][ n FF nx ⋅⋅⋅ = ) 2cos( ])[ 1(][ n FF nxm nx ⋅⋅⋅ ⋅ ⋅+= ) 2cos ...](https://img.yumpu.com/19534764/1/184x260/2cos-n-ff-nx-2cos-1-n-ff-nxm-nx-2cos-.jpg?quality=85)

![Wersja pełna [8,55 MB] - Wydział Elektroniki, Telekomunikacji i ...](https://img.yumpu.com/19534759/1/184x260/wersja-pelna-855-mb-wydzial-elektroniki-telekomunikacji-i-.jpg?quality=85)