PXA3xx Design Guide - Marvell

PXA3xx Design Guide - Marvell

PXA3xx Design Guide - Marvell

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

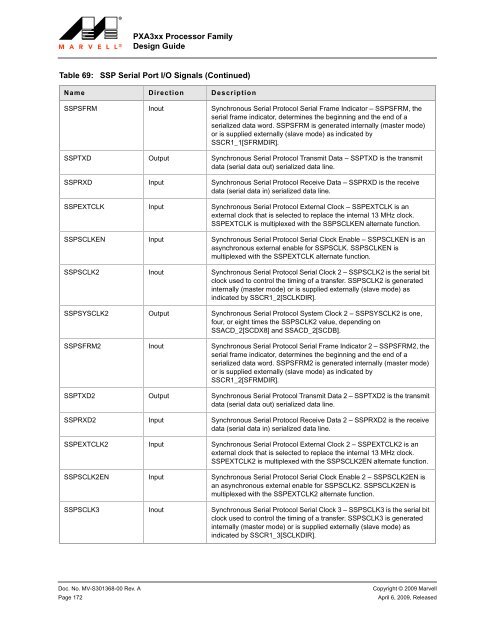

<strong>PXA3xx</strong> Processor Family<strong>Design</strong> <strong>Guide</strong>Table 69:SSP Serial Port I/O Signals (Continued)Name Direction DescriptionSSPSFRM Inout Synchronous Serial Protocol Serial Frame Indicator – SSPSFRM, theserial frame indicator, determines the beginning and the end of aserialized data word. SSPSFRM is generated internally (master mode)or is supplied externally (slave mode) as indicated bySSCR1_1[SFRMDIR].SSPTXD Output Synchronous Serial Protocol Transmit Data – SSPTXD is the transmitdata (serial data out) serialized data line.SSPRXD Input Synchronous Serial Protocol Receive Data – SSPRXD is the receivedata (serial data in) serialized data line.SSPEXTCLK Input Synchronous Serial Protocol External Clock – SSPEXTCLK is anexternal clock that is selected to replace the internal 13 MHz clock.SSPEXTCLK is multiplexed with the SSPSCLKEN alternate function.SSPSCLKEN Input Synchronous Serial Protocol Serial Clock Enable – SSPSCLKEN is anasynchronous external enable for SSPSCLK. SSPSCLKEN ismultiplexed with the SSPEXTCLK alternate function.SSPSCLK2 Inout Synchronous Serial Protocol Serial Clock 2 – SSPSCLK2 is the serial bitclock used to control the timing of a transfer. SSPSCLK2 is generatedinternally (master mode) or is supplied externally (slave mode) asindicated by SSCR1_2[SCLKDIR].SSPSYSCLK2 Output Synchronous Serial Protocol System Clock 2 – SSPSYSCLK2 is one,four, or eight times the SSPSCLK2 value, depending onSSACD_2[SCDX8] and SSACD_2[SCDB].SSPSFRM2 Inout Synchronous Serial Protocol Serial Frame Indicator 2 – SSPSFRM2, theserial frame indicator, determines the beginning and the end of aserialized data word. SSPSFRM2 is generated internally (master mode)or is supplied externally (slave mode) as indicated bySSCR1_2[SFRMDIR].SSPTXD2 Output Synchronous Serial Protocol Transmit Data 2 – SSPTXD2 is the transmitdata (serial data out) serialized data line.SSPRXD2 Input Synchronous Serial Protocol Receive Data 2 – SSPRXD2 is the receivedata (serial data in) serialized data line.SSPEXTCLK2 Input Synchronous Serial Protocol External Clock 2 – SSPEXTCLK2 is anexternal clock that is selected to replace the internal 13 MHz clock.SSPEXTCLK2 is multiplexed with the SSPSCLK2EN alternate function.SSPSCLK2EN Input Synchronous Serial Protocol Serial Clock Enable 2 – SSPSCLK2EN isan asynchronous external enable for SSPSCLK2. SSPSCLK2EN ismultiplexed with the SSPEXTCLK2 alternate function.SSPSCLK3 Inout Synchronous Serial Protocol Serial Clock 3 – SSPSCLK3 is the serial bitclock used to control the timing of a transfer. SSPSCLK3 is generatedinternally (master mode) or is supplied externally (slave mode) asindicated by SSCR1_3[SCLKDIR].Doc. No. MV-S301368-00 Rev. A Copyright © 2009 <strong>Marvell</strong>Page 172April 6, 2009, Released