8x300 design guide - Al Kossow's Bitsavers - Trailing-Edge

8x300 design guide - Al Kossow's Bitsavers - Trailing-Edge

8x300 design guide - Al Kossow's Bitsavers - Trailing-Edge

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

PRODUCT IDENTITY<br />

aT32- Three-state, field-programmable<br />

(addresses 0-255), synchronous<br />

user port<br />

aX32- Three-state, preprogrammed addresses<br />

(0-15), synchronous user<br />

port in slim-line (0.4 in.) package<br />

aT33- Open-collector, synchronous user<br />

port<br />

aT35- Open-collector, asynchronous<br />

user port<br />

aT36- Three-state, field-programmable<br />

(addresses 0-255), asynchronous<br />

user port<br />

aX36- Three-state, preprogrammed addresses<br />

(0-15), asynchronous user<br />

port In slim-line (0.4 in.) package<br />

aX42- Three-state, 4-inputl4-output, preprogrammed<br />

addresses (0-15),<br />

synchronous user port<br />

ORDERING INFORMATION<br />

<strong>Al</strong>l of the above parts can be ordered as<br />

field-programmable or with addresses preassigned<br />

at the factory. To order, use the<br />

following part-number format.<br />

N8XYY-ZZZ-P<br />

N8TYY-ZZZ-P<br />

where,<br />

P = F for Ceramic package and<br />

NA for Plastic package<br />

ZZZ = Any address from 000 through 255 (decimalJ-256<br />

available addresses·for each 8T-- part. For an ax-<br />

part, preassigned addresses are limited to 000<br />

through 015 (decimalJ-16 available addresses.<br />

YY = 1/0 port version.<br />

FEATURES<br />

• Dual bidirectional ports (except SX42)<br />

• Independent port operation (user-port<br />

priority for data entry)<br />

• User data input available as synchronous<br />

(ST32/aX32/aX42/aT33) or as asynchronous<br />

(aT35/aT36/aX36)<br />

• User data bus available with three-state<br />

(aT32/aX32, aT36/aX36, and/or aX42) or<br />

open-collector (aT33 and/or aT35) outputs<br />

• At power-up, user-port outputs are high<br />

and microprocessor-port outputs are<br />

high-z; status latch (from address compare)<br />

is also cleared at power-up<br />

• Three-state TTL outputs for high-drive<br />

capabilities<br />

• Directly compatible with aX300 microcontroller<br />

• Single +5V supply<br />

• Slim (0.4 in.) 24-pin DIP (aX32/<br />

aX36/aX42 only)<br />

A stock of 8T32s and 8T36s with addresses<br />

"1" through "10" are maintained in inventory;<br />

with a longer lead time, a small quantity<br />

of addresses "11" through "50" are also<br />

available.<br />

113211133!113S/1136<br />

111211136,'1142<br />

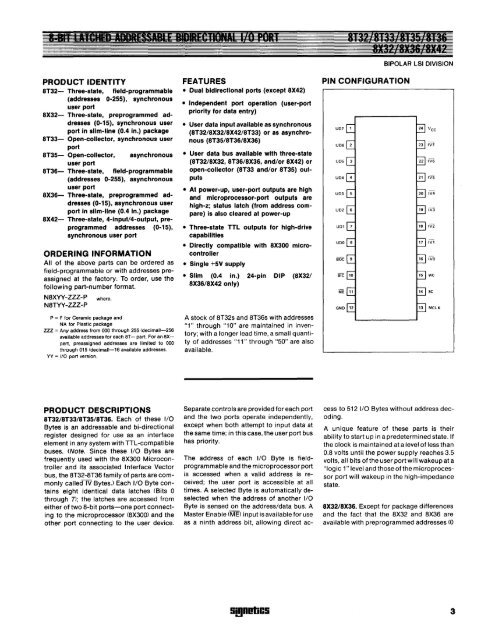

PIN CONFIGURATION<br />

BIPOLAR LSI DIVISION<br />

UD7 1 24 VCC<br />

UD6 2 23 IV7<br />

UD5 3 22 IV6<br />

UD4 4 21 IV5<br />

UD3 5 20 IV4<br />

UD2 6 19 IV3<br />

UD1 7 18 IV2<br />

UDO 8 17 IV1<br />

BOC 9 16 IVO<br />

BIC 10 15 WC<br />

ME 11 14 SC<br />

GND 12 13 MCLK<br />

PRODUCT DESCRIPTIONS<br />

aT32JST33/ST35/ST36. Each of these I/O<br />

Bytes is an addressable and bi-directional<br />

register <strong>design</strong>ed for use as an interface<br />

element in any system with TTL-compatible<br />

buses. (Note. Since these I/O Bytes are<br />

frequently used with the 8X300 Microcontroller<br />

and its associated Interface Vector<br />

bus, the 8T32-8T36 family of parts are commonly<br />

callecfW Bytes') Each I/O Byte contains<br />

eight identical data latches (Bits 0<br />

through 7); the latches are accessed from<br />

either of two 8-bit ports-one port connecting<br />

to the microprocessor (8X30Q) and the<br />

other port connecting to the user device.<br />

Separate controls are provided for each port<br />

and the two ports operate independently,<br />

except when both attempt to input data at<br />

the same time; in this case, the user port bus<br />

has priority.<br />

The address of each 110 Byte is fieldprogrammable<br />

and the microprocessor port<br />

is accessed when a valid address is received;<br />

the user port is accessible at all<br />

times. A. selected Byte is automatically deselected<br />

when the address of another I/O<br />

Byte is sensed on the address/data bus. A<br />

Master Enable (ME) input is available for use<br />

as a ninth address bit, allowing direct ae-<br />

cess to 512 I/O Bytes without address decoding.<br />

A unique feature of these parts is their<br />

ability to start up in a predetermined state. If<br />

the clock is maintained at a level of less than<br />

0.8 volts until the power supply reaches 3.5<br />

volts, all bits of the user port will wakeup at a<br />

"logic 1" level and those of the microprocessor<br />

port will wakeup in the high-impedance<br />

state.<br />

aX32/aX36. Except for package differences<br />

and the fact that the 8X32 and 8X36 are<br />

available with preprogrammed addresses (0<br />

!ijgIOliC!i<br />

3