8x300 design guide - Al Kossow's Bitsavers - Trailing-Edge

8x300 design guide - Al Kossow's Bitsavers - Trailing-Edge

8x300 design guide - Al Kossow's Bitsavers - Trailing-Edge

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

I<br />

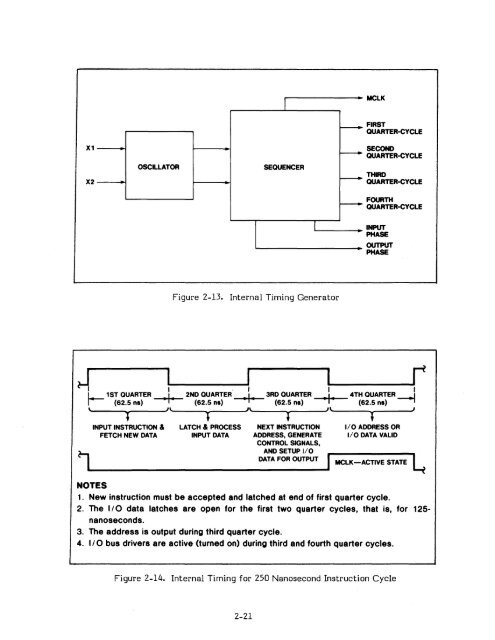

MCLK<br />

----.<br />

FIRST<br />

QUARTER-CYCLE<br />

X1<br />

----.<br />

SECOND<br />

OUARTER-CYCLE<br />

X2<br />

OSCILLATOR<br />

SEQUENCER<br />

----.<br />

THIRD<br />

OUARTER-CYCLE<br />

----.<br />

FOURTH<br />

OUARTER-CYCLE<br />

I<br />

INPUT<br />

PHASE<br />

OUTPUT<br />

PHASE<br />

Figure 2-13. Internal Timing Generator<br />

I<br />

~ I I<br />

~ 1 ST QUARTER _I_ 2ND QUARTER _I_ 3RD QUARTER ~_""I"<br />

l<br />

-----..r<br />

____<br />

__ 4TH QUARTER _------1<br />

r-<br />

\~________________ (62.5 ns)<br />

JJ~ __________<br />

(62.5 ns)<br />

/~__________<br />

(62.5 ns)<br />

J~ ___________ (62.5<br />

~<br />

ns) __________ -----. JJ<br />

1 l J l<br />

INPUT INSTRUCTION &<br />

FETCH NEW DATA<br />

LATCH & PROCESS<br />

INPUT DATA<br />

NEXT INSTRUCTION<br />

ADDRESS, GENERATE<br />

CONTROL SIGNALS,<br />

AND SETUP 1/0<br />

DATA FOR OUTPUT<br />

~--------<br />

1/ 0 ADDRESS OR<br />

1/0 DATA VALID<br />

MCLK-ACTIVE STATE ~<br />

NOTES<br />

1. New instruction must be accepted and latched at end of first quarter cycle.<br />

2. The 110 data latches are open for the first two quarter cycles, that is, for 125-<br />

nanoseconds.<br />

3. The address is output during third quarter cycle.<br />

4. 110 bus drivers are active (turned on) during third and fourth quarter cycles.<br />

Figure 2-14. Internal Timing for 250 Nanosecond Instruction Cycle<br />

2-21