8x300 design guide - Al Kossow's Bitsavers - Trailing-Edge

8x300 design guide - Al Kossow's Bitsavers - Trailing-Edge

8x300 design guide - Al Kossow's Bitsavers - Trailing-Edge

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

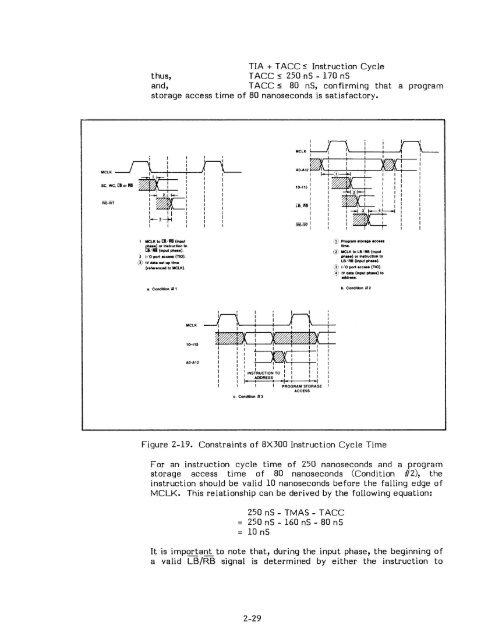

TIA + TACC ~ Instruction Cycle<br />

thus,<br />

T ACC s 250 nS - 170 nS<br />

and,<br />

T ACC:s 80 nS, confirming that a program<br />

storage access time of 80 nanoseconds is satisfactory.<br />

MCLK<br />

,,-'" ~_J ! ii<br />

I<br />

I<br />

:::, ~ i !'---+-i ---+E--:-'1:<br />

I<br />

tJtt<br />

2 1 .1 II<br />

I I :: I<br />

:_"1 ":<br />

[8, JIB I I I I:<br />

I I I<br />

iVii-M I I I I<br />

I<br />

I<br />

1 MCLK to [l/JIB (Input<br />

ph ••• ) or In.tructlon to<br />

[l/Jili (Input ph ••• ).<br />

2 1/0 port ecc ••• (TIO).<br />

® IV dat ••• t-up tim.<br />

(r.t.r.nced to MCLK).<br />

•. Condition # 1<br />

CD Progr.m .tor.g •• cc ...<br />

tim •.<br />

@ MCLK to LB/RS (Input<br />

ph ••• ) or In.tructlon to<br />

LB/RS (Input phe •• ).<br />

® 1/0 port ecc ••• (TIO).<br />

.1) IV del. (Input ph ••• ) to<br />

eddr ....<br />

b. Condition # 2<br />

MCLK<br />

10-115<br />

AO-AI2<br />

~ i I I: I<br />

~:~<br />

I I I I I<br />

III~<br />

II<br />

I i ! I I I I I I I I<br />

I I I I I<br />

I I I I I I<br />

INSTRUCTION TO: I I I<br />

fDDRESSI • I' : : • I :<br />

I I PROGRAM STORAGE I<br />

ACCESS<br />

c. Condition # 3<br />

Figure 2-19. Constraints of 8X300 Instruction Cycle Time<br />

F or an instruction cycle time of 250 nanoseconds and a program<br />

storage access time of 80 nanoseconds (Condition 112), the<br />

instruction should be valid 10 nanoseconds before the falling edge of<br />

MCLK. This relationship can be derived by the following equation:<br />

250 nS - TMAS - T ACC<br />

= 250 nS - 160 nS - 80 nS<br />

= 10 nS<br />

It is important to note that, during the input phase, the beginning of<br />

a valid LB/RB signal is determined by either the instruction to<br />

2-29