8x300 design guide - Al Kossow's Bitsavers - Trailing-Edge

8x300 design guide - Al Kossow's Bitsavers - Trailing-Edge

8x300 design guide - Al Kossow's Bitsavers - Trailing-Edge

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

2.5.2 Interrupt Control (Handshake)<br />

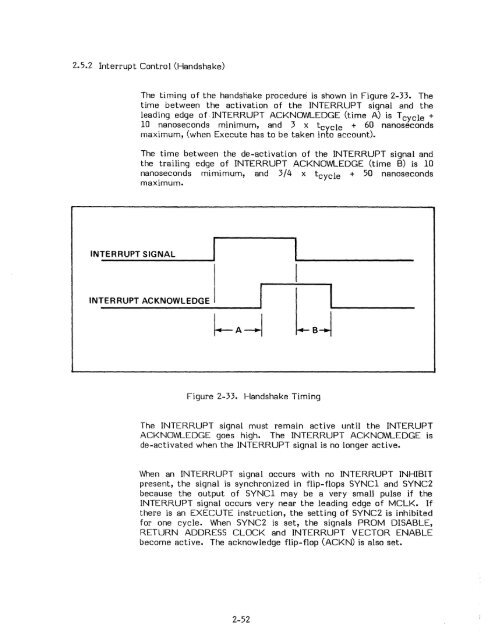

The timing of the handshake procedure is shown in Figure 2-33. The<br />

time between the activation of the INTERRUPT signal and the<br />

leading edge of -INTERRUPT ACKNOWLEDGE (time A) is T cycle +<br />

10 nanoseconds minimum, and 3 x tc cle + 60 nanoseconds<br />

maximum, (when Execute has to be taken inro account).<br />

The time between the de-activation of the INTERRUPT signal and<br />

the trailing edge of INTERRUPT ACKNOWLEDGE (time B) is 10<br />

nanoseconds mimimum, and 3/4 x tcycle + 50 nanoseconds<br />

maximum.<br />

INTERRUPT SIGNAL<br />

INTERRUPT ACKNOWLEDGE<br />

Figure 2-33. Handshake Timing<br />

The INTERRUPT signal must remain active until the INTERUPT<br />

ACKNOWLEDGE goes high. The INTERRUPT ACKNOWLEDGE is<br />

de-activated when the INTERRUPT signal is no longer active.<br />

\Nhen an INTERRUPT signal occurs with no INTERRUPT INHIBIT<br />

present, the signal is synchronized in flip-flops SYNC 1 and SYNC2<br />

because the output of SYNC1 may be a very small pulse if the<br />

INTERRUPT signal occurs very near the leading edge of MCLK. If<br />

there is an EXECUTE instruction, the setting of SYNC2 is inhibited<br />

for one cycle. When SYNC2 is set, the signals PROM DISABLE,<br />

RETURN ADDRESS CLOCK and INTERRUPT VECTOR ENABLE<br />

become active. The acknowledge flip-flop (ACKN) is also set.<br />

2-52