Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

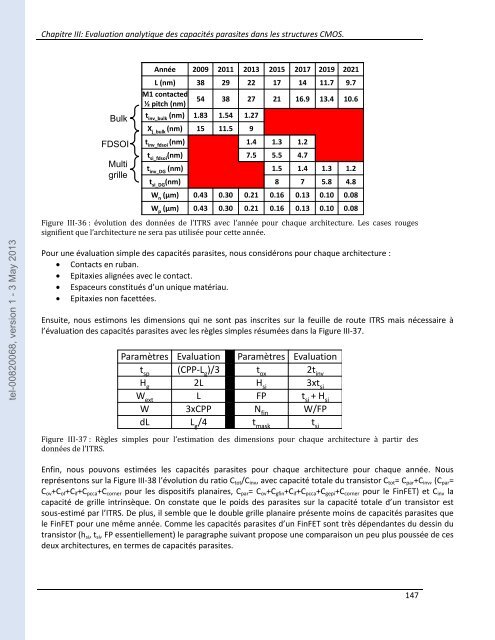

Chapitre III: Evaluation analytique <strong>de</strong>s capacités parasites dans les structures CMOS.<br />

Bulk<br />

FDSOI<br />

Multi<br />

grille<br />

Année 2009 2011 2013 2015 2017 2019 2021<br />

L (nm) 38 29 22 17 14 11.7 9.7<br />

M1 contacted<br />

½ pitch (nm)<br />

54 38 27 21 16.9 13.4 10.6<br />

t inv_bulk<br />

(nm) 1.83 1.54 1.27<br />

X j_bulk<br />

(nm) 15 11.5 9<br />

t inv_fdsoi<br />

(nm) 1.4 1.3 1.2<br />

t si_fdsoi<br />

(nm) 7.5 5.5 4.7<br />

t inv_DG<br />

(nm) 1.5 1.4 1.3 1.2<br />

t si_DG<br />

(nm) 8 7 5.8 4.8<br />

W n<br />

(µm) 0.43 0.30 0.21 0.16 0.13 0.10 0.08<br />

W p<br />

(µm) 0.43 0.30 0.21 0.16 0.13 0.10 0.08<br />

Figure III-36 : évolution <strong>de</strong>s données <strong>de</strong> l’ITRS avec l’année <strong>pour</strong> chaque architecture. Les cases rouges<br />

signifient que l’architecture ne sera pas utilisée <strong>pour</strong> cette année.<br />

tel-00820068, version 1 - 3 May 2013<br />

Pour une évaluation simple <strong>de</strong>s capacités parasites, nous considérons <strong>pour</strong> chaque architecture :<br />

Contacts en ruban.<br />

Epitaxies alignées avec le contact.<br />

Espaceurs constitués d’un unique matériau.<br />

Epitaxies non facettées.<br />

Ensuite, nous estimons les dimensions qui ne sont pas inscrites sur la feuille <strong>de</strong> route ITRS mais nécessaire à<br />

l’évaluation <strong>de</strong>s capacités parasites avec les règles simples résumées dans la Figure III-37.<br />

Paramètres Evaluation Paramètres Evaluation<br />

t sp<br />

(CPP-L g<br />

)/3 t ox<br />

2t inv<br />

H g<br />

2L H si<br />

3xt si<br />

W ext<br />

L FP t si<br />

+ H si<br />

W 3xCPP N fin<br />

W/FP<br />

dL L g<br />

/4 t mask<br />

t si<br />

Figure III-37 : Règles simples <strong>pour</strong> l’estimation <strong>de</strong>s dimensions <strong>pour</strong> chaque architecture à partir <strong>de</strong>s<br />

données <strong>de</strong> l’ITRS.<br />

Enfin, nous pouvons estimées les capacités parasites <strong>pour</strong> chaque architecture <strong>pour</strong> chaque année. Nous<br />

représentons sur la Figure III-38 l’évolution du ratio C tot /C inv , avec capacité totale du transistor C tot = C par +C inv , (C par =<br />

C ov +C of +C if +C pcca +C corner <strong>pour</strong> les dispositifs planaires, C par = C ov +C gfin +C if +C pcca +C gepi +C corner <strong>pour</strong> le FinFET) et C inv la<br />

capacité <strong>de</strong> grille intrinsèque. On constate que le poids <strong>de</strong>s parasites sur la capacité totale d’un transistor est<br />

sous-estimé par l’ITRS. De plus, il semble que le double grille planaire présente moins <strong>de</strong> capacités parasites que<br />

le FinFET <strong>pour</strong> une même année. Comme les capacités parasites d’un FinFET sont très dépendantes du <strong>de</strong>ssin du<br />

transistor (h si , t si , FP essentiellement) le paragraphe suivant propose une comparaison un peu plus poussée <strong>de</strong> ces<br />

<strong>de</strong>ux architectures, en termes <strong>de</strong> capacités parasites.<br />

147