Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapitre V: Evaluation <strong>de</strong>s <strong>performances</strong> avec <strong>de</strong>s outils <strong>de</strong> CAO conventionnels.<br />

Leur évaluation est très complexe à effectuer <strong>de</strong> manière analytique et nous choisirons alors d’utiliser un outil<br />

d’extraction automatique <strong>de</strong>s parasites dans les interconnexions : le PEX (<strong>pour</strong> Parasitics EXtraction). A partir du<br />

<strong>de</strong>ssin du circuit, et <strong>de</strong>s règles <strong>de</strong> <strong>de</strong>ssin <strong>de</strong>s interconnexions, le PEX fournit les valeurs d’un circuit équivalent RC,<br />

qui va permettre la prise en compte <strong>de</strong> la perte <strong>de</strong> vitesse due aux interconnexions, et donc permettre une<br />

évaluation plus réaliste, tant sur la vitesse que sur la consommation dynamique d’un circuit.<br />

Ce type d’évaluation étant très complexe, nous avons dû utiliser ce qui était à disposition au moment <strong>de</strong> l’étu<strong>de</strong>,<br />

à savoir le PEX développé <strong>pour</strong> l’architecture conventionnelle sur substrat massif du nœud 20nm. Nous avons<br />

considéré que les parasites liés aux interconnexions étaient les mêmes, quelle que soit l’architecture <strong>de</strong>s<br />

transistors composant les circuits.<br />

tel-00820068, version 1 - 3 May 2013<br />

V.A.5. Définition <strong>de</strong> source <strong>de</strong> variation aléatoire <strong>de</strong>s paramètres<br />

technologiques <strong>pour</strong> prise en compte <strong>de</strong> la variabilité.<br />

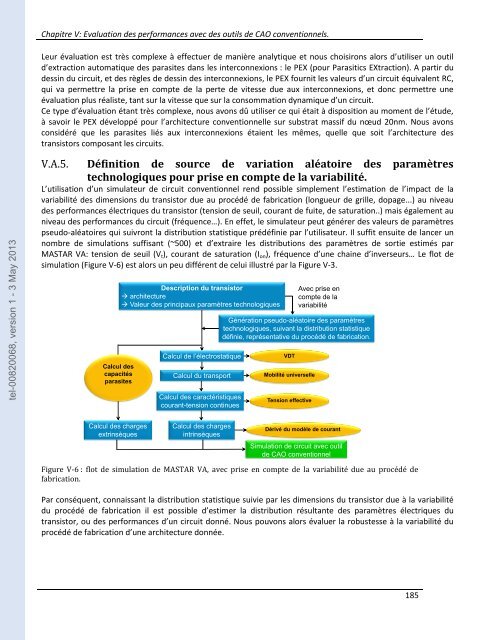

L’utilisation d’un simulateur <strong>de</strong> circuit conventionnel rend possible simplement l’estimation <strong>de</strong> l’impact <strong>de</strong> la<br />

variabilité <strong>de</strong>s dimensions du transistor due au procédé <strong>de</strong> fabrication (longueur <strong>de</strong> grille, dopage...) au niveau<br />

<strong>de</strong>s <strong>performances</strong> électriques du transistor (tension <strong>de</strong> seuil, courant <strong>de</strong> fuite, <strong>de</strong> saturation..) mais également au<br />

niveau <strong>de</strong>s <strong>performances</strong> du circuit (fréquence…). En effet, le simulateur peut générer <strong>de</strong>s valeurs <strong>de</strong> paramètres<br />

pseudo-aléatoires qui suivront la distribution statistique prédéfinie par l’utilisateur. Il suffit ensuite <strong>de</strong> lancer un<br />

nombre <strong>de</strong> simulations suffisant (~500) et d’extraire les distributions <strong>de</strong>s paramètres <strong>de</strong> sortie estimés par<br />

MASTAR VA: tension <strong>de</strong> seuil (V t ), courant <strong>de</strong> saturation (I on ), fréquence d’une chaine d’inverseurs… Le flot <strong>de</strong><br />

simulation (Figure V-6) est alors un peu différent <strong>de</strong> celui illustré par la Figure V-3.<br />

Calcul <strong>de</strong>s<br />

capacités<br />

parasites<br />

Description du transistor<br />

architecture<br />

Valeur <strong>de</strong>s principaux paramètres technologiques<br />

Calcul <strong>de</strong> l’électrostatique<br />

Calcul du transport<br />

Calcul <strong>de</strong>s caractéristiques<br />

courant-tension continues<br />

VDT<br />

Mobilité universelle<br />

Tension effective<br />

Avec prise en<br />

compte <strong>de</strong> la<br />

variabilité<br />

Génération pseudo-aléatoire <strong>de</strong>s paramètres<br />

technologiques, suivant la distribution statistique<br />

définie, représentative du procédé <strong>de</strong> fabrication.<br />

Calcul <strong>de</strong>s charges<br />

extrinsèques<br />

Calcul <strong>de</strong>s charges<br />

intrinsèques<br />

Dérivé du modèle <strong>de</strong> courant<br />

Simulation <strong>de</strong> circuit avec outil<br />

<strong>de</strong> CAO conventionnel<br />

Figure V-6 : flot <strong>de</strong> simulation <strong>de</strong> MASTAR VA, avec prise en compte <strong>de</strong> la variabilité due au procédé <strong>de</strong><br />

fabrication.<br />

Par conséquent, connaissant la distribution statistique suivie par les dimensions du transistor due à la variabilité<br />

du procédé <strong>de</strong> fabrication il est possible d’estimer la distribution résultante <strong>de</strong>s paramètres électriques du<br />

transistor, ou <strong>de</strong>s <strong>performances</strong> d’un circuit donné. Nous pouvons alors évaluer la robustesse à la variabilité du<br />

procédé <strong>de</strong> fabrication d’une architecture donnée.<br />

185