Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapitre I: Le transistor MOSFET: fonctionnement, miniaturisation et architectures.<br />

I.C.2.<br />

Réduction <strong>de</strong> la longueur <strong>de</strong> grille<br />

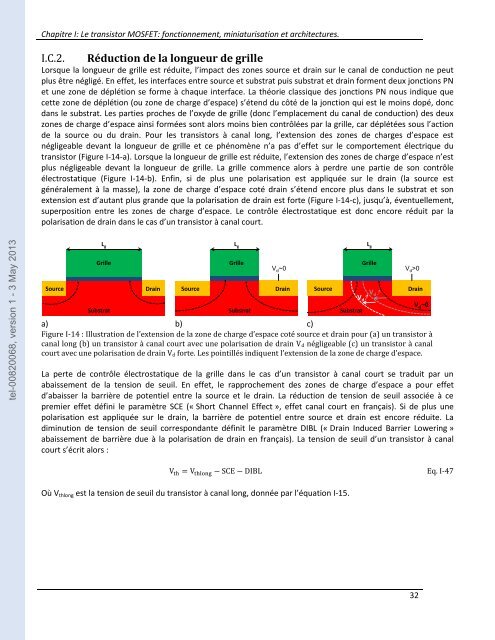

Lorsque la longueur <strong>de</strong> grille est réduite, l’impact <strong>de</strong>s zones source et drain sur le canal <strong>de</strong> conduction ne peut<br />

plus être négligé. En effet, les interfaces entre source et substrat puis substrat et drain forment <strong>de</strong>ux jonctions PN<br />

et une zone <strong>de</strong> déplétion se forme à chaque interface. La théorie classique <strong>de</strong>s jonctions PN nous indique que<br />

cette zone <strong>de</strong> déplétion (ou zone <strong>de</strong> charge d’espace) s’étend du côté <strong>de</strong> la jonction qui est le moins dopé, donc<br />

dans le substrat. Les parties proches <strong>de</strong> l’oxy<strong>de</strong> <strong>de</strong> grille (donc l’emplacement du canal <strong>de</strong> conduction) <strong>de</strong>s <strong>de</strong>ux<br />

zones <strong>de</strong> charge d’espace ainsi formées sont alors moins bien contrôlées par la grille, car déplétées sous l’action<br />

<strong>de</strong> la source ou du drain. Pour les transistors à canal long, l’extension <strong>de</strong>s zones <strong>de</strong> charges d’espace est<br />

négligeable <strong>de</strong>vant la longueur <strong>de</strong> grille et ce phénomène n’a pas d’effet sur le comportement électrique du<br />

transistor (Figure I-14-a). Lorsque la longueur <strong>de</strong> grille est réduite, l’extension <strong>de</strong>s zones <strong>de</strong> charge d’espace n’est<br />

plus négligeable <strong>de</strong>vant la longueur <strong>de</strong> grille. La grille commence alors à perdre une partie <strong>de</strong> son contrôle<br />

électrostatique (Figure I-14-b). Enfin, si <strong>de</strong> plus une polarisation est appliquée sur le drain (la source est<br />

généralement à la masse), la zone <strong>de</strong> charge d’espace coté drain s’étend encore plus dans le substrat et son<br />

extension est d’autant plus gran<strong>de</strong> que la polarisation <strong>de</strong> drain est forte (Figure I-14-c), jusqu’à, éventuellement,<br />

superposition entre les zones <strong>de</strong> charge d’espace. Le contrôle électrostatique est donc encore réduit par la<br />

polarisation <strong>de</strong> drain dans le cas d’un transistor à canal court.<br />

tel-00820068, version 1 - 3 May 2013<br />

Source<br />

L g<br />

Grille<br />

Substrat<br />

Drain<br />

Source<br />

L g<br />

Grille<br />

Substrat<br />

a) b) c)<br />

Figure I-14 : Illustration <strong>de</strong> l’extension <strong>de</strong> la zone <strong>de</strong> charge d’espace coté source et drain <strong>pour</strong> (a) un transistor à<br />

canal long (b) un transistor à canal court avec une polarisation <strong>de</strong> drain V d négligeable (c) un transistor à canal<br />

court avec une polarisation <strong>de</strong> drain V d forte. Les pointillés indiquent l’extension <strong>de</strong> la zone <strong>de</strong> charge d’espace.<br />

La perte <strong>de</strong> contrôle électrostatique <strong>de</strong> la grille dans le cas d’un transistor à canal court se traduit par un<br />

abaissement <strong>de</strong> la tension <strong>de</strong> seuil. En effet, le rapprochement <strong>de</strong>s zones <strong>de</strong> charge d’espace a <strong>pour</strong> effet<br />

d’abaisser la barrière <strong>de</strong> potentiel entre la source et le drain. La réduction <strong>de</strong> tension <strong>de</strong> seuil associée à ce<br />

premier effet défini le paramètre SCE (« Short Channel Effect », effet canal court en français). Si <strong>de</strong> plus une<br />

polarisation est appliquée sur le drain, la barrière <strong>de</strong> potentiel entre source et drain est encore réduite. La<br />

diminution <strong>de</strong> tension <strong>de</strong> seuil correspondante définit le paramètre DIBL (« Drain Induced Barrier Lowering »<br />

abaissement <strong>de</strong> barrière due à la polarisation <strong>de</strong> drain en français). La tension <strong>de</strong> seuil d’un transistor à canal<br />

court s’écrit alors :<br />

V d ~0<br />

Drain<br />

Source<br />

V d<br />

Substrat<br />

L g<br />

Grille<br />

V d<br />

V d >0<br />

Drain<br />

V d ~0<br />

Eq. I-47<br />

Où V thlong est la tension <strong>de</strong> seuil du transistor à canal long, donnée par l’équation I-15.<br />

32