Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapitre V: Evaluation <strong>de</strong>s <strong>performances</strong> avec <strong>de</strong>s outils <strong>de</strong> CAO conventionnels.<br />

V.A.2.<br />

Flot <strong>de</strong> simulation<br />

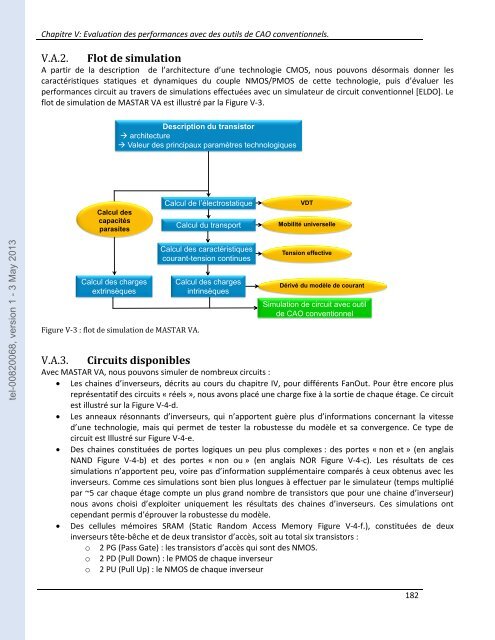

A partir <strong>de</strong> la <strong>de</strong>scription <strong>de</strong> l’architecture d’une technologie CMOS, nous pouvons désormais donner les<br />

caractéristiques statiques et dynamiques du couple NMOS/PMOS <strong>de</strong> cette technologie, puis d’évaluer les<br />

<strong>performances</strong> circuit au travers <strong>de</strong> simulations effectuées avec un simulateur <strong>de</strong> circuit conventionnel [ELDO]. Le<br />

flot <strong>de</strong> simulation <strong>de</strong> MASTAR VA est illustré par la Figure V-3.<br />

Description du transistor<br />

architecture<br />

Valeur <strong>de</strong>s principaux paramètres technologiques<br />

Calcul <strong>de</strong>s<br />

capacités<br />

parasites<br />

Calcul <strong>de</strong> l’électrostatique<br />

Calcul du transport<br />

VDT<br />

Mobilité universelle<br />

tel-00820068, version 1 - 3 May 2013<br />

Figure V-3 : flot <strong>de</strong> simulation <strong>de</strong> MASTAR VA.<br />

V.A.3.<br />

Calcul <strong>de</strong>s charges<br />

extrinsèques<br />

Circuits disponibles<br />

Calcul <strong>de</strong>s caractéristiques<br />

courant-tension continues<br />

Calcul <strong>de</strong>s charges<br />

intrinsèques<br />

Tension effective<br />

Dérivé du modèle <strong>de</strong> courant<br />

Simulation <strong>de</strong> circuit avec outil<br />

<strong>de</strong> CAO conventionnel<br />

Avec MASTAR VA, nous pouvons simuler <strong>de</strong> nombreux circuits :<br />

Les chaines d’inverseurs, décrits au cours du chapitre IV, <strong>pour</strong> différents FanOut. Pour être encore plus<br />

représentatif <strong>de</strong>s circuits « réels », nous avons placé une charge fixe à la sortie <strong>de</strong> chaque étage. Ce circuit<br />

est illustré sur la Figure V-4-d.<br />

Les anneaux résonnants d’inverseurs, qui n’apportent guère plus d’informations concernant la vitesse<br />

d’une technologie, mais qui permet <strong>de</strong> tester la robustesse du modèle et sa convergence. Ce type <strong>de</strong><br />

circuit est Illustré sur Figure V-4-e.<br />

Des chaines constituées <strong>de</strong> portes logiques un peu plus complexes : <strong>de</strong>s portes « non et » (en anglais<br />

NAND Figure V-4-b) et <strong>de</strong>s portes « non ou » (en anglais NOR Figure V-4-c). Les résultats <strong>de</strong> ces<br />

simulations n’apportent peu, voire pas d’information supplémentaire comparés à ceux obtenus avec les<br />

inverseurs. Comme ces simulations sont bien plus longues à effectuer par le simulateur (temps multiplié<br />

par ~5 car chaque étage compte un plus grand nombre <strong>de</strong> transistors que <strong>pour</strong> une chaine d’inverseur)<br />

nous avons choisi d’exploiter uniquement les résultats <strong>de</strong>s chaines d’inverseurs. Ces simulations ont<br />

cependant permis d’éprouver la robustesse du modèle.<br />

Des cellules mémoires SRAM (Static Random Access Memory Figure V-4-f.), constituées <strong>de</strong> <strong>de</strong>ux<br />

inverseurs tête-bêche et <strong>de</strong> <strong>de</strong>ux transistor d’accès, soit au total six transistors :<br />

o 2 PG (Pass Gate) : les transistors d’accès qui sont <strong>de</strong>s NMOS.<br />

o 2 PD (Pull Down) : le PMOS <strong>de</strong> chaque inverseur<br />

o 2 PU (Pull Up) : le NMOS <strong>de</strong> chaque inverseur<br />

182