Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

DIBL (mV)<br />

DIBL (mV)<br />

DIBL (mV)<br />

DIBL(mV)<br />

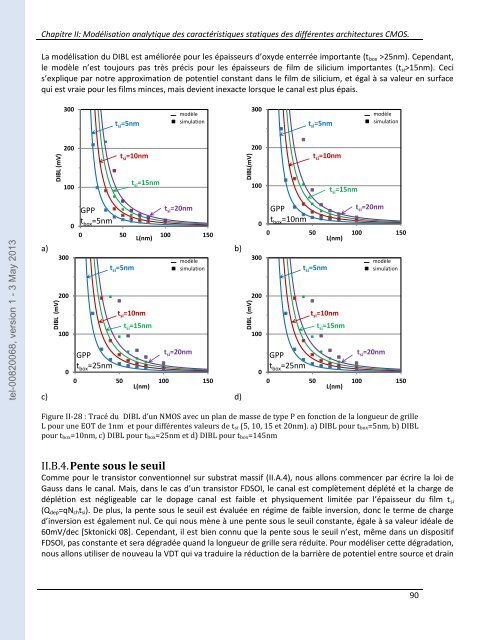

Chapitre II: Modélisation analytique <strong>de</strong>s caractéristiques statiques <strong>de</strong>s différentes architectures CMOS.<br />

La modélisation du DIBL est améliorée <strong>pour</strong> les épaisseurs d’oxy<strong>de</strong> enterrée importante (t box >25nm). Cependant,<br />

le modèle n’est toujours pas très précis <strong>pour</strong> les épaisseurs <strong>de</strong> film <strong>de</strong> silicium importantes (t si >15nm). Ceci<br />

s’explique par notre approximation <strong>de</strong> potentiel constant dans le film <strong>de</strong> silicium, et égal à sa valeur en surface<br />

qui est vraie <strong>pour</strong> les films minces, mais <strong>de</strong>vient inexacte lorsque le canal est plus épais.<br />

300<br />

t si =5nm<br />

modèle<br />

simulation<br />

300<br />

t si =5nm<br />

modèle<br />

simulation<br />

200<br />

t si =10nm<br />

200<br />

t si =10nm<br />

100<br />

t si =15nm<br />

100<br />

t si =15nm<br />

tel-00820068, version 1 - 3 May 2013<br />

0<br />

GPP<br />

t box =5nm<br />

t si =20nm<br />

0 50<br />

L(nm)<br />

100 150<br />

a) b)<br />

300<br />

200<br />

100<br />

0<br />

GPP<br />

t box =25nm<br />

t si =5nm<br />

t si =10nm<br />

t si =15nm<br />

t si =20nm<br />

modèle<br />

simulation<br />

0 50 100 150<br />

L(nm)<br />

c) d)<br />

0<br />

300<br />

200<br />

100<br />

0<br />

GPP<br />

t box =10nm<br />

t si =20nm<br />

0 50 100 150<br />

L(nm)<br />

GPP<br />

t box =25nm<br />

t si =5nm<br />

t si =10nm<br />

t si =15nm<br />

t si =20nm<br />

modèle<br />

simulation<br />

0 50 100 150<br />

L(nm)<br />

Figure II-28 : Tracé du DIBL d’un NMOS avec un plan <strong>de</strong> masse <strong>de</strong> type P en fonction <strong>de</strong> la longueur <strong>de</strong> grille<br />

L <strong>pour</strong> une EOT <strong>de</strong> 1nm et <strong>pour</strong> différentes valeurs <strong>de</strong> t si (5, 10, 15 et 20nm). a) DIBL <strong>pour</strong> t box=5nm, b) DIBL<br />

<strong>pour</strong> t box=10nm, c) DIBL <strong>pour</strong> t box=25nm et d) DIBL <strong>pour</strong> t box=145nm<br />

II.B.4. Pente sous le seuil<br />

Comme <strong>pour</strong> le transistor conventionnel sur substrat massif (II.A.4), nous allons commencer par écrire la loi <strong>de</strong><br />

Gauss dans le canal. Mais, dans le cas d’un transistor FDSOI, le canal est complètement déplété et la charge <strong>de</strong><br />

déplétion est négligeable car le dopage canal est faible et physiquement limitée par l’épaisseur du film t si<br />

(Q <strong>de</strong>p =qN ch t si ). De plus, la pente sous le seuil est évaluée en régime <strong>de</strong> faible inversion, donc le terme <strong>de</strong> charge<br />

d’inversion est également nul. Ce qui nous mène à une pente sous le seuil constante, égale à sa valeur idéale <strong>de</strong><br />

60mV/<strong>de</strong>c [Sktonicki 08]. Cependant, il est bien connu que la pente sous le seuil n’est, même dans un dispositif<br />

FDSOI, pas constante et sera dégradée quand la longueur <strong>de</strong> grille sera réduite. Pour modéliser cette dégradation,<br />

nous allons utiliser <strong>de</strong> nouveau la VDT qui va traduire la réduction <strong>de</strong> la barrière <strong>de</strong> potentiel entre source et drain<br />

90