Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapitre I: Le transistor MOSFET: fonctionnement, miniaturisation et architectures.<br />

polarisation V ds appliquée, ce qui entraine une réduction du courant <strong>de</strong> saturation. Diverses métho<strong>de</strong>s sont<br />

proposées <strong>pour</strong> en tenir compte dans la littérature [Gautier 03] [Taur 98], nous en détaillerons une au cours du<br />

chapitre V.<br />

Contact<br />

L g<br />

Grille<br />

X j<br />

Siliciure<br />

Source<br />

Substrat<br />

Drain<br />

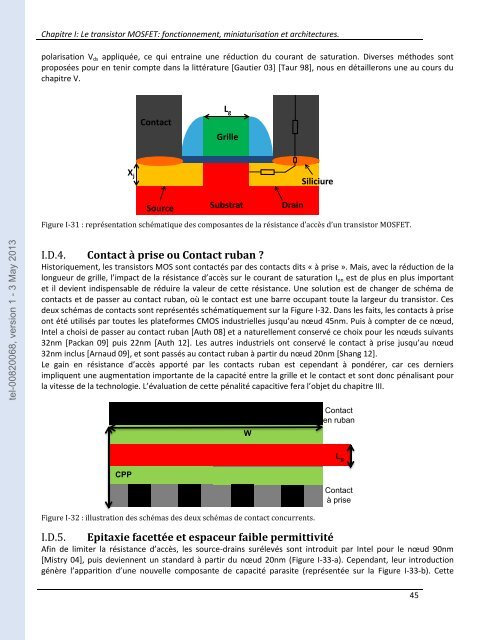

Figure I-31 : représentation schématique <strong>de</strong>s composantes <strong>de</strong> la résistance d’accès d’un transistor MOSFET.<br />

tel-00820068, version 1 - 3 May 2013<br />

I.D.4.<br />

Contact à prise ou Contact ruban ?<br />

Historiquement, les transistors MOS sont contactés par <strong>de</strong>s contacts dits « à prise ». Mais, avec la réduction <strong>de</strong> la<br />

longueur <strong>de</strong> grille, l’impact <strong>de</strong> la résistance d’accès sur le courant <strong>de</strong> saturation I on est <strong>de</strong> plus en plus important<br />

et il <strong>de</strong>vient indispensable <strong>de</strong> réduire la valeur <strong>de</strong> cette résistance. Une solution est <strong>de</strong> changer <strong>de</strong> schéma <strong>de</strong><br />

contacts et <strong>de</strong> passer au contact ruban, où le contact est une barre occupant toute la largeur du transistor. Ces<br />

<strong>de</strong>ux schémas <strong>de</strong> contacts sont représentés schématiquement sur la Figure I-32. Dans les faits, les contacts à prise<br />

ont été utilisés par toutes les plateformes CMOS industrielles jusqu’au nœud 45nm. Puis à compter <strong>de</strong> ce nœud,<br />

Intel a choisi <strong>de</strong> passer au contact ruban [Auth 08] et a naturellement conservé ce choix <strong>pour</strong> les nœuds suivants<br />

32nm [Packan 09] puis 22nm [Auth 12]. Les autres industriels ont conservé le contact à prise jusqu’au nœud<br />

32nm inclus [Arnaud 09], et sont passés au contact ruban à partir du nœud 20nm [Shang 12].<br />

Le gain en résistance d’accès apporté par les contacts ruban est cependant à pondérer, car ces <strong>de</strong>rniers<br />

impliquent une augmentation importante <strong>de</strong> la capacité entre la grille et le contact et sont donc pénalisant <strong>pour</strong><br />

la vitesse <strong>de</strong> la technologie. L’évaluation <strong>de</strong> cette pénalité capacitive fera l’objet du chapitre III.<br />

W<br />

Contact<br />

en ruban<br />

L g<br />

CPP<br />

Contact<br />

à prise<br />

Figure I-32 : illustration <strong>de</strong>s schémas <strong>de</strong>s <strong>de</strong>ux schémas <strong>de</strong> contact concurrents.<br />

I.D.5.<br />

Epitaxie facettée et espaceur faible permittivité<br />

Afin <strong>de</strong> limiter la résistance d’accès, les source-drains surélevés sont introduit par Intel <strong>pour</strong> le nœud 90nm<br />

[Mistry 04], puis <strong>de</strong>viennent un standard à partir du nœud 20nm (Figure I-33-a). Cependant, leur introduction<br />

génère l’apparition d’une nouvelle composante <strong>de</strong> capacité parasite (représentée sur la Figure I-33-b). Cette<br />

45