Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Ioff (nA/µm)<br />

Ioff (nA/µm)<br />

Ioff (nA/µm)<br />

Ioff (nA/µm)<br />

Chapitre V: Evaluation <strong>de</strong>s <strong>performances</strong> avec <strong>de</strong>s outils <strong>de</strong> CAO conventionnels.<br />

V.B.3.<br />

Comparaison <strong>de</strong>s <strong>performances</strong> statiques<br />

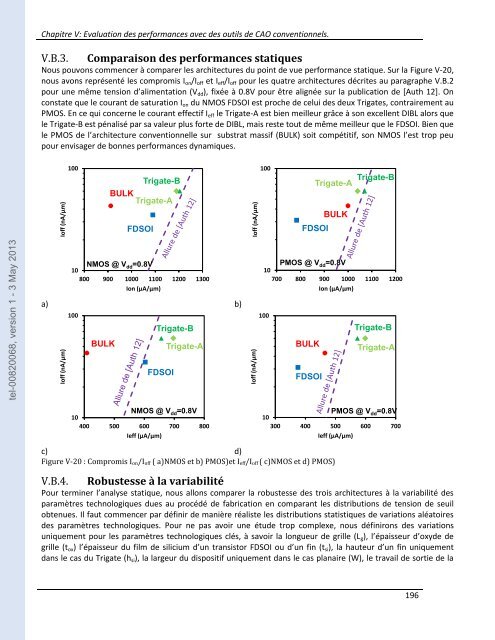

Nous pouvons commencer à comparer les architectures du point <strong>de</strong> vue performance statique. Sur la Figure V-20,<br />

nous avons représenté les compromis I on /I off et I eff /I off <strong>pour</strong> les quatre architectures décrites au paragraphe V.B.2<br />

<strong>pour</strong> une même tension d’alimentation (V dd ), fixée à 0.8V <strong>pour</strong> être alignée sur la publication <strong>de</strong> [Auth 12]. On<br />

constate que le courant <strong>de</strong> saturation I on du NMOS FDSOI est proche <strong>de</strong> celui <strong>de</strong>s <strong>de</strong>ux Trigates, contrairement au<br />

PMOS. En ce qui concerne le courant effectif I eff le Trigate-A est bien meilleur grâce à son excellent DIBL alors que<br />

le Trigate-B est pénalisé par sa valeur plus forte <strong>de</strong> DIBL, mais reste tout <strong>de</strong> même meilleur que le FDSOI. Bien que<br />

le PMOS <strong>de</strong> l’architecture conventionnelle sur substrat massif (BULK) soit compétitif, son NMOS l’est trop peu<br />

<strong>pour</strong> envisager <strong>de</strong> bonnes <strong>performances</strong> dynamiques.<br />

100<br />

Trigate-B<br />

BULK<br />

Trigate-A<br />

100<br />

Trigate-A<br />

Trigate-B<br />

BULK<br />

FDSOI<br />

FDSOI<br />

tel-00820068, version 1 - 3 May 2013<br />

NMOS @ V dd =0.8V<br />

10<br />

800 900 1000 1100 1200 1300<br />

Ion (µA/µm)<br />

a) b)<br />

100<br />

Trigate-B<br />

BULK<br />

Trigate-A<br />

FDSOI<br />

PMOS @ V dd =0.8V<br />

10<br />

700 800 900 1000 1100 1200<br />

Ion (µA/µm)<br />

100<br />

Trigate-B<br />

BULK<br />

Trigate-A<br />

FDSOI<br />

c) d)<br />

Figure V-20 : Compromis I on/I off ( a)NMOS et b) PMOS)et I eff/I off ( c)NMOS et d) PMOS)<br />

V.B.4.<br />

10<br />

NMOS @ V dd =0.8V<br />

400 500 600 700 800<br />

Ieff (µA/µm)<br />

Robustesse à la variabilité<br />

10<br />

PMOS @ V dd =0.8V<br />

300 400 500 600 700<br />

Ieff (µA/µm)<br />

Pour terminer l’analyse statique, nous allons comparer la robustesse <strong>de</strong>s trois architectures à la variabilité <strong>de</strong>s<br />

paramètres technologiques dues au procédé <strong>de</strong> fabrication en comparant les distributions <strong>de</strong> tension <strong>de</strong> seuil<br />

obtenues. Il faut commencer par définir <strong>de</strong> manière réaliste les distributions statistiques <strong>de</strong> variations aléatoires<br />

<strong>de</strong>s paramètres technologiques. Pour ne pas avoir une étu<strong>de</strong> trop complexe, nous définirons <strong>de</strong>s variations<br />

uniquement <strong>pour</strong> les paramètres technologiques clés, à savoir la longueur <strong>de</strong> grille (L g ), l’épaisseur d’oxy<strong>de</strong> <strong>de</strong><br />

grille (t ox ) l’épaisseur du film <strong>de</strong> silicium d’un transistor FDSOI ou d’un fin (t si ), la hauteur d’un fin uniquement<br />

dans le cas du Trigate (h si ), la largeur du dispositif uniquement dans le cas planaire (W), le travail <strong>de</strong> sortie <strong>de</strong> la<br />

196